If you would like to cite any of this material, please use the following:

**S. Palermo**, "CMOS Nanoelectronics Analog and RF VLSI Circuits. Chapter 9: High-Speed Serial I/O Design for Channel-Limited and Power-Constrained Systems," McGraw-Hill, 2011.

## PART 2

### **High-Speed Circuits**

#### CHAPTER 9

High-Speed Serial I/O Design for Channel-Limited and Power-Constrained Systems

#### CHAPTER 10

CDMA-Based Crosstalk Cancellation Technique for High-Speed Chip-to-Chip Communication

#### **CHAPTER 11**

EqualizationTechniques for High-Speed Serial Data Links

#### **CHAPTER 12**

$\Delta\Sigma$  Fractional-N Phase-Locked Loop

#### CHAPTER 13

Design and Applications of Delay-Locked Loops

#### CHAPTER 14

Digital Clock Generators Used for Nanometer Processors and Memories MCGH205-Iniewski

June 27, 2011

7:15

## CHAPTER 9

# High-Speed Serial I/O Design for Channel-Limited and Power-Constrained Systems

Samuel Palermo

Texas A&M University

#### 9.1 Introduction

Dramatic increases in processing power, fueled by a combination of *integrated circuit* (IC) scaling and shifts in computer architectures from single-core to future many-core systems, have rapidly scaled onchip aggregate bandwidths into the Tb/s range,<sup>1</sup> necessitating a corresponding increase in the amount of data communicated between chips not to limit overall system performance.<sup>2</sup> Due to the limited *input/output* (I/O) pin count in chip packages and *printed circuit board* (PCB) wiring constraints, high-speed serial link technology is employed for this interchip communication.

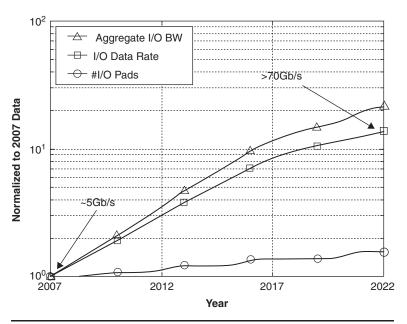

The two conventional methods to increase interchip communication bandwidth include raising both the per-channel data rate and the I/O number, as projected in the current *International Technology Roadmap for Semiconductors* (ITRS) roadmap (Fig. 9.1). However, packaging limitations prevent a dramatic increase in I/O channel number. This implies that chip-to-chip data rates must increase dramatically in the next decade, presenting quite a challenge considering the limited power budgets in processors. While high-performance I/O circuitry can leverage the technology improvements that enable increased core performance, unfortunately the bandwidth of the electrical channels used for interchip communication has not scaled

FIGURE 9.1 I/O scaling projections. (From Ref. 6.)

in the same manner. Thus, rather than being technology limited, current high-speed I/O link designs are becoming channel limited. In order to continue scaling data rates, link designers implement sophisticated equalization circuitry to compensate for the frequency-dependent loss of the band-limited channels.<sup>3–5</sup> But along with this additional complexity come both power and area costs, necessitating advances in low-power serial I/O design techniques and consideration of alternate I/O technologies, such as optical interchip communication links.

This chapter discusses the challenges associated with scaling serial I/O data rates and current design techniques. Section 9.2, "High-Speed Link Overview," describes the major high-speed components, channel properties, and performance metrics. A presentation of equalization and advanced modulation techniques follows in Sec. 9.3, "Channel-Limited Design Techniques." Link architectures and circuit techniques that improve link power efficiency are discussed in Sec. 9.4, "Low-Power Design Techniques." Section 9.5, "Optical Interconnects," details how optical interchip communication links have the potential to fully leverage increased data rates provided through CMOS technology scaling at suitable power efficiency levels. Finally, the chapter is summarized in the "Conclusion."

#### 9.2 High-Speed Link Overview

High-speed point-to-point electrical link systems employ specialized I/O circuitry that performs incident wave signaling over carefully designed controlled-impedance channels in order to achieve high data rates. As will be described later in this section, the electrical channel's frequency-dependent loss and impedance discontinuities become major limiters in data rate scaling.

This section begins by describing the three major link circuit components: (1) the transmitter, (2) the receiver, and (3) the timing system. Next, the section discusses the electrical channel properties that impact the transmitted signal. The section concludes by providing an overview of key technology and system performance metrics.

#### 9.2.1 Electrical Link Circuits

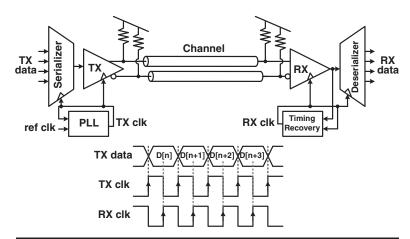

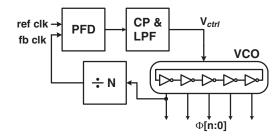

Figure 9.2 shows the major components of a typical high-speed electrical link system. Due to the limited number of high-speed I/O pins in chip packages and PCB wiring constraints, a high-bandwidth transmitter serializes parallel input data for transmission. Differential low-swing signaling is commonly employed for common-mode noise rejection and reduced crosstalk due to the inherent signal current return path. At the receiver, the incoming signal is sampled, regenerated to CMOS values, and deserialized. The high-frequency clocks that synchronize the data transfer onto the channel are generated by a frequency synthesis *phase-locked loop* (PLL) at the transmitter, while at the receiver the sampling clocks are aligned to the incoming data stream by a *timing recovery system*.

Figure 9.2 High-speed electrical link system.

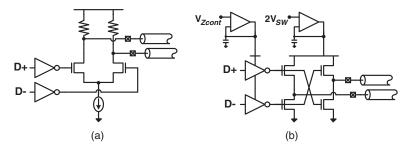

Figure 9.3 Transmitter output stages: (a) current-mode driver and (b) voltage-mode driver.

#### **Transmitter**

The transmitter must generate an accurate voltage swing on the channel while also maintaining proper output impedance in order to attenuate any channel-induced reflections. Either current- or voltage-mode drivers, shown in Fig. 9.3, are suitable output stages. Current-mode drivers typically steer current close to 20 mA between the differential channel lines in order to launch a bipolar voltage swing on the order of ±500 mV. Driver output impedance is maintained through termination, which is in parallel with the high-impedance current switch. While current-mode drivers are most commonly implemented, the power associated with the required output voltage for proper transistor output impedance and the "wasted" current in the parallel termination led designers to consider voltage-mode drivers. These drivers use a regulated output stage to supply a fixed output swing on the channel through a series termination that is feedback controlled.<sup>9</sup> While the feedback impedance control is not as simple as parallel termination, the voltage-mode drivers have the potential to supply an equal receiver voltage swing at a quarter<sup>10</sup> of the common 20 mA cost of current-mode drivers.

#### Receiver

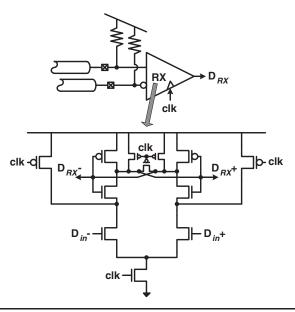

Figure 9.4 shows a high-speed receiver that compares the incoming data to a threshold and amplifies the signal to a CMOS value. This highlights a major advantage of binary differential signaling, where this threshold is inherent, whereas single-ended signaling requires careful threshold generation to account for variations in signal amplitude, loss, and noise. <sup>11</sup> The bulk of the signal amplification is often performed with a positive feedback latch. <sup>12,13</sup> These latches are more power efficient versus cascaded linear amplification stages since they do not dissipate DC current. While regenerative latches are the most power-efficient input amplifiers, link designers have used a small number of linear preamplification stages to implement equalization filters that offset channel loss faced by high data rate signals. <sup>14,15</sup>

291

FIGURE 9.4 Receiver input stage with regenerative latch. (From Ref. 12.)

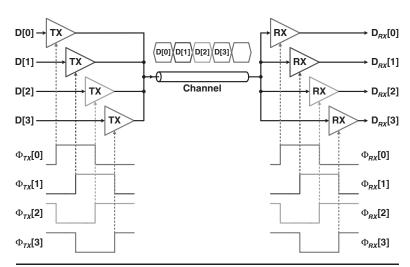

One issue with these latches is that they require time to reset or "precharge," and thus, to achieve high data rates, often multiple latches are placed in parallel at the input and activated with multiple clock phases spaced a bit period apart in a time-division-demultiplexing manner, <sup>16,17</sup> shown in Fig. 9.5. This technique is also

FIGURE 9.5 Time-division multiplexing link.

applicable at the transmitter, where the maximum serialized data rate is set by the clocks switching the multiplexer. The use of multiple clock phases offset in time by a bit period can overcome the intrinsic gate-speed, which limits the maximum clock rate that can be efficiently distributed to a period of 6–8 fan-out of four (FO4) clock buffer delays. <sup>18</sup>

#### **Timing System**

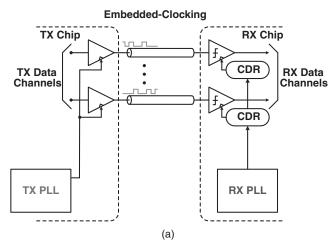

The two primary clocking architectures employed in high-speed I/O systems are *embedded clocking* and *source synchronous clocking*, as shown in Fig. 9.6. While both architectures typically use a *phase-locked loop*

**Figure 9.6** Multichannel serial link system: (a) embedded-clocking architecture and (b) source synchronous clocking architecture.

293

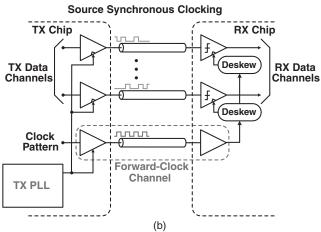

**FIGURE 9.7** PLL frequency synthesizer.

(PLL) to generate the transmit serialization clocks, they differ in the manner in which receiver timing recovery is performed. In embedded clocking systems, only I/O data channels are routed to the receiver, where a *clock-and-data recovery* (CDR) system extracts clock information "embedded" in the transmitted data stream to determine the receiver clock frequency and optimum phase position. Source synchronous systems, also called *forwarded-clock systems*, use an additional dedicated clock channel to forward the high-frequency serialization clock used by multiple transmit channels to the receiver chip, where per-channel de-skewing circuitry is implemented. The circuits and architectural trade-offs of these timing systems are discussed next.

Figure 9.7 shows a PLL, which is often used at the transmitter for clock synthesis in order to serialize reduced-rate parallel input data and also potentially at the receiver for clock recovery. The PLL is a negative feedback loop that works to lock the phase of the feedback clock to an input reference clock. A phase-frequency detector produces an error signal proportional to the phase difference between the feedback and reference clocks. This phase error is then filtered to provide a control signal to a *voltage-controlled oscillator* (VCO), which generates the output clock. The PLL performs frequency synthesis by placing a clock divider in the feedback path, which forces the loop to lock with the output clock frequency equal to the input reference frequency times the loop division factor.

It is important that the PLL produce clocks with low timing noise, quantified in the timing domain as jitter and in the frequency domain as phase noise. Considering this, the most critical PLL component is the VCO, as its phase noise performance can dominate at the output clock and have a large influence on the overall loop design. LC oscillators typically have the best phase noise performance, but their area is large and tuning range is limited. While ring oscillators display inferior phase noise characteristics, they offer advantages in reduced area, wide frequency range, and an ability to easily generate multiple phase clocks for time-division multiplexing applications. 16,17

Also important is the PLL's ability to maintain proper operation over process variances, operating voltage, temperature, and frequency

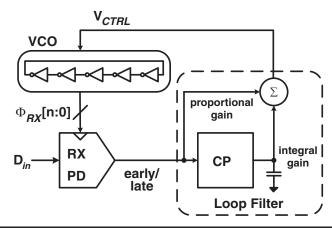

FIGURE 9.8 PLL-based CDR system.

range. To address this, self-biasing techniques were developed by Maneatis<sup>20</sup> (and expanded in Refs. 21 and 22) that set constant loop stability and noise filtering parameters over these variances in operating conditions.

At the receiver, timing recovery is required in order to position the data sampling clocks with maximum timing margin. For embedded clocking systems, it is possible to modify a PLL to perform clock recovery with changes in the phase detection circuitry, as shown in Fig. 9.8. Here the phase detector samples the incoming data stream to extract both data and phase information.

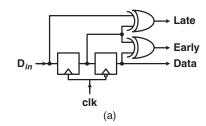

As shown in Fig. 9.9, the phase detector can either be linear,<sup>23</sup> which provides both sign and magnitude information of the phase error, or binary,<sup>24</sup> which provides only phase error sign information. While CDR systems with linear phase detectors are easier to analyze, generally they are harder to implement at high data rates due to the difficulty of generating narrow error pulse widths, resulting in effective dead zones in the phase detector.<sup>25</sup> Binary, or "bang-bang," phase detectors minimize this problem by providing equal delay for both data and phase information and only resolving the sign of the phase error.<sup>26</sup>

While a PLL-based CDR is an effective timing recover system, the power and area cost of having a PLL for each receive channel is prohibitive in some I/O systems. Another issue is that CDR bandwidth is often set by jitter transfer and tolerance specifications, leaving little freedom to optimize PLL bandwidth to filter various sources of clock noise, such as VCO phase noise. The nonlinear behavior of binary phase detectors can also lead to limited locking range, necessitating a parallel frequency acquisition loop.<sup>27</sup> This motivates the use of dual-loop clock recovery,<sup>11</sup> which allows several channels to share a global receiver PLL locked to a stable reference clock and also provides two

295

FIGURE 9.9 CDR phase detectors: (a) linear (from Ref. 23) and (b) binary (from Ref. 24).

degrees of freedom to independently set the CDR bandwidth for a given specification and optimize the receiver PLL bandwidth for best jitter performance.

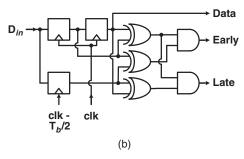

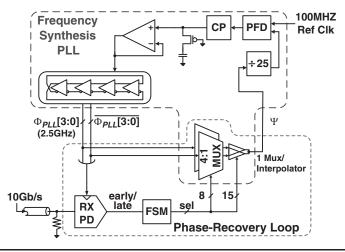

An implementation of a dual-loop CDR is shown in Fig. 9.10. This CDR has a core loop which produces several clock phases for a separate phase recovery loop. The core loop can either be a frequency synthesis PLL<sup>28</sup> or, if frequency synthesis is done elsewhere, a lower-complexity *delay-locked loop* (DLL). An independent phase recovery loop provides flexibility in the input jitter tracking without any effect on the core loop dynamics, and allows for sharing of the clock generation with the transmit channels. The phase loop typically consists of a binary phase detector, a digital loop filter, and a *finite state machine* (FSM) that updates the phase muxes and interpolators to generate the optimal position for the receiver clocks. Low-swing current-controlled differential buffers<sup>11</sup> or large-swing tristate digital buffers<sup>29</sup> are used to implement the interpolators.

Phase interpolator linearity, which is both a function of the interpolator design and the input clocks' phase precision, can have a major impact on CDR timing margin and phase error tracking. The interpolator must be designed with a proper ratio between the input phase spacing and the interpolator output time constant in order to insure proper phase mixing. Also, while there is the potential to share the core loop among multiple receiver channels, distributing the multiple clock phases in a manner that preserves precise phase spacing can result in significant power consumption. In order to avoid distributing multiple clock phases, the global frequency synthesis PLL can distribute one clock phase to local DLLs, either placed at each

7:15

#### 296 High-Speed Circuits

Dual-loop CDR for a 4:1 input demultiplexing receiver. FIGURE 9.10

channel or shared by a cluster of receive channels, which generate the multiple clock phases used for interpolation.<sup>30,31</sup> This architecture can be used for source-synchronous systems by replacing the global PLL clock with the incoming forwarded clock.30

While proper design of these high-speed I/O components requires considerable attention, CMOS scaling allows the basic circuit blocks to achieve data rates that exceed 10 Gb/s. 14,32 However, as data rates scale into the low gigabits-per-second, the frequency-dependent loss of the chip-to-chip electrical wires disperses the transmitted signal to the extent that it is undetectable at the receiver without proper signal processing or channel-equalization techniques. Thus, in order to design systems that achieve increased data rates, link designers must comprehend the high-frequency characteristics of the electrical channel, which are outlined next.

#### 9.2.2 Electrical Channels

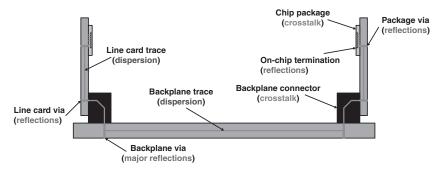

Electrical interchip communication bandwidth is predominantly limited by high-frequency loss of electrical traces, reflections caused

FIGURE 9.11 Backplane system cross-section.

from impedance discontinuities, and adjacent signal crosstalk, as shown in Fig. 9.11. The relative magnitudes of these channel characteristics depend on the length and quality of the electrical channel, which is a function of the application. Common applications range from processor-to-memory interconnections, which typically have short (<10-in.) top-level microstrip traces with relatively uniform loss slopes, <sup>14</sup> to server/router and multiprocessor systems, which employ either long ( $\sim$ 30-in.) multilayer backplanes or ( $\sim$ 10 m) cables, <sup>33</sup> which can both possess large impedance discontinuities and loss.

PCB traces suffer from high-frequency attenuation caused by the wire skin effect and dielectric loss. As a signal propagates down a transmission line, the normalized amplitude at a distance *x* is equal to

$$\frac{V(x)}{V(0)} = e^{-(\alpha_R + \alpha_D)x},\tag{9.1}$$

where  $\alpha_R$  and  $\alpha_D$  represent resistive and dielectric loss factors.<sup>7</sup> The *skin effect*, which describes the process of high-frequency signal current crowding near the conductor surface, impacts the resistive loss term as frequency increases. This results in a resistive loss term that is proportional to the square-root of frequency

$$\alpha_R = \frac{R_{AC}}{2Z_0} = \frac{2.61 \times 10^{-7} \sqrt{\rho_r}}{\pi D 2Z_0} \sqrt{f},$$

(9.2)

where D is the trace's diameter (in.),  $\rho$  is the relative resistivity compared to copper, and  $Z_0$  is the trace's characteristic impedance.<sup>34</sup> Dielectric loss describes the process where energy is absorbed from the signal trace and transferred into heat due to the rotation of the board's dielectric atoms in an alternating electric field.<sup>34</sup> This results in the dielectric loss term increasing proportional to the signal frequency

$$\alpha_D = \frac{\pi\sqrt{\varepsilon_r}\tan\delta_D}{c}f,\tag{9.3}$$

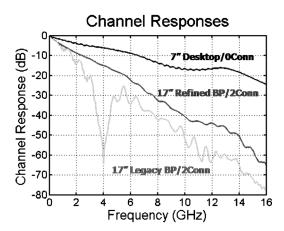

Figure 9.12

Frequency

response of

several channels.

where  $\varepsilon_r$  is the relative permittivity, c is the speed of light, and  $\tan \delta_D$  is the board material's loss tangent.<sup>15</sup>

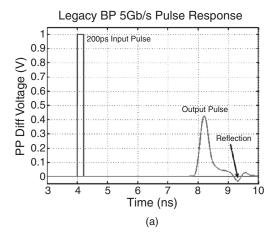

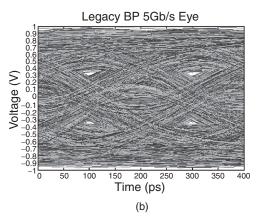

Figure 9.12 shows how these frequency-dependent loss terms result in low-pass channels where the attenuation increases with distance. The high-frequency content of pulses sent across these channels is filtered, resulting in an attenuated received pulse with energy that has been dispersed over several bit periods, as shown in Fig. 9.13 (a). When transmitting data across the channel, energy from individual bits will now interfere with adjacent bits and make them more difficult to detect. This *intersymbol interference* (ISI) increases with channel loss and can completely close the received data eye diagram, as shown in Fig. 9.13 (b).

Signal interference also results from reflections caused by impedance discontinuities. If a signal propagating across a transmission line experiences a change in impedance  $Z_r$  relative to the line's characteristic impedance  $Z_0$ , a percentage of that signal equal to

$$\frac{V_r}{V_i} = \frac{Z_r - Z_0}{Z_r + Z_0} \tag{9.4}$$

will reflect back to the transmitter. This results in an attenuated or, in the case of multiple reflections, a time-delayed version of the signal arriving at the receiver. The most common sources of impedance discontinuities are from on-chip termination mismatches and via stubs that result with signaling over multiple PCB layers. Figure 9.12 shows that the capacitive discontinuity formed by the thick backplane via stubs can cause severe nulls in the channel frequency response.

Another form of interference comes from crosstalk, which occurs due to both capacitive and inductive coupling between neighboring signal lines. As a signal propagates across the channel, it experiences the most crosstalk in the backplane connectors and chip packages

299

FIGURE 9.13

Legacy backplane channel performance at 5 Gb/s: (a) pulse response and (b) eye diagram.

where the signal spacing is smallest compared to the distance to a shield. Crosstalk is classified either as *near-end crosstalk* (NEXT), where energy from an aggressor (transmitter) couples and is reflected back to the victim (receiver) on the same chip, or *far-end crosstalk* (FEXT), where the aggressor energy couples and propagates along the channel to a victim on another chip. NEXT is commonly the most detrimental crosstalk, as energy from a strong transmitter ( $\sim 1\,\mathrm{V}_{pp}$ ) can couple onto a received signal at the same chip, which has been attenuated ( $\sim 20\,\mathrm{mV}_{pp}$ ) from propagating on the lossy channel. Crosstalk is potentially a major limiter to high-speed electrical link scaling, since in common backplane channels the crosstalk energy can actually exceed the through channel signal energy at frequencies near 4 GHz.<sup>3</sup>

#### **9.2.3 Performance Metrics**

The high-speed link data rate can be limited by both circuit technology and the communication channel. Aggressive CMOS technology

scaling has benefited both digital and analog circuit performance, with 45-nm processes displaying sub-20-ps inverter *fan-out of four* (FO4) delays and being capable of measured nMOS  $f_T$  near 400 GHz.<sup>35</sup>

As mentioned earlier, one of the key circuit constraints to increasing the data rate is the maximum clock frequency that can be effectively distributed, which is a period of 6–8 FO4 clock buffer delays. This implies that a half-rate link architecture can potentially achieve a minimum bit period of 3–4 FO4, or greater than 12 Gb/s in a 45-nm technology, with relatively simple inverter-based clock distribution. While technology scaling should allow the data rate to increase proportionally with improvements in gate delay, the limited electrical channel bandwidth is actually the major constraint in the majority of systems, with overall channel loss and equalization complexity limiting the maximum data rate to lower than the potential offered by a given technology.

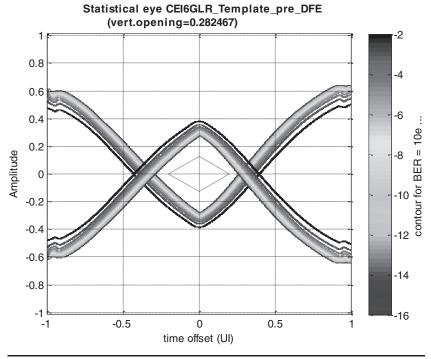

The primary serial link performance metric is the *bit-error-rate* (BER), with systems requiring BERs ranging from  $10^{-12}$  to  $10^{-15}$ . In order to meet these BER targets, link system design must consider both the channel and all relevant noise sources. Link modeling and

**Figure 9.14** Six gigabits-per-second statistical BER eye produced with StatEye simulator.

analysis tools have matured rapidly as data rates have significantly exceeded electrical channel bandwidth. Current state-of-the-art link analysis tools<sup>36–38</sup> use statistical means to combine deterministic noise sources, such as ISI and bounded supply noise and jitter, random noise sources, such as Gaussian thermal noise and jitter, and receiver aperture in order to estimate link margins at a given BER. The results of a link analysis tool can be visualized with a statistical BER eye (Fig. 9.14) which gives the overall link voltage and timing margins at a given BER.

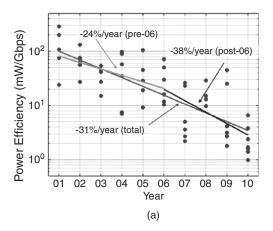

Another metric under increased emphasis is power efficiency, expressed by the link power consumption divided by the data rate in units of mW/Gb/s or pJ/bit. This is due to systems demanding a rapid increase in I/O bandwidth, while also facing power ceilings. As shown in Fig. 9.15, the majority of link architectures exceed 10 mW/Gb/s. This is a consequence of several reasons, including complying with

FIGURE 9.15

High-speed serial I/O trends: (a)

power efficiency vs.

year and (b) power

efficiency vs. data

rate.

industry standards, supporting demanding channel loss, and placing emphasis on extending raw data rate. Recent work has emphasized reducing link power, <sup>15,30,39</sup> with designs achieving sub-3 mW/Gb/s at data rates up to 12.5 Gb/s.

#### 9.3 Channel-Limited Design Techniques

The previous section discussed interference mechanisms that can severely limit the rate at which data is transmitted across electrical channels. As shown in Fig. 9.13, frequency-dependent channel loss can reach magnitudes sufficient to make simple NRZ binary signaling undetectable. Thus, in order to continue scaling electrical link data rates, designers have implemented systems that compensate for frequency-dependent loss or equalize the channel response. This section discusses how the equalization circuitry is often implemented in high-speed links, as well as other approaches for dealing with these issues.

#### 9.3.1 Equalization Systems

In order to extend a given channel's maximum data rate, many communication systems use equalization techniques to cancel intersymbol interference caused by channel distortion. Equalizers are implemented either as linear filters (both discrete and continuous-time) that attempt to flatten the channel frequency response, or as nonlinear filters that directly cancel ISI based on the received data sequence. Depending on system data rate requirements relative to channel bandwidth and the severity of potential noise sources, different combinations of transmit and/or receive equalization are employed.

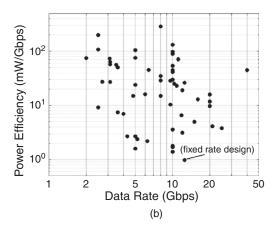

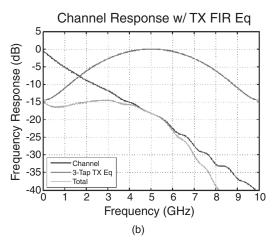

Transmit equalization, implemented with a *finite impulse response* (FIR) filter, is the most common technique used in high-speed links. <sup>40</sup> This TX "pre-emphasis" (or more accurately "de-emphasis") filter, shown in Fig. 9.16, attempts to invert the channel distortion that a data bit experiences by predistorting or shaping the pulse over several bit times. While this filtering could also be implemented at the receiver, the main advantage of implementing the equalization at the transmitter is that it is generally easier to build high-speed *digital-to-analog converters* (DACs) versus receive-side analog-to-digital converters. However, because the transmitter is limited in the amount of peak power that it can send across the channel due to driver voltage headroom constraints, the net result is that the low-frequency signal content has been attenuated down to the high-frequency level, as shown in Fig. 9.16.

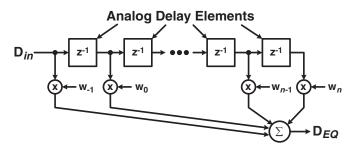

Figure 9.17 shows a block diagram of receiver-side FIR equalization. A common problem faced by linear receiver-side equalization is that high-frequency noise content and crosstalk are amplified along

#### High-Speed Serial I/O Design 303

FIGURE 9.16 TX equalization with an FIR filter.

FIGURE 9.17 RX equalization with an FIR filter.

FIGURE 9.18 Continuous-time equalizing amplifier.

with the incoming signal. Also challenging is the implementation of the analog delay elements, which are often implemented through time-interleaved sample-and-hold stages<sup>41</sup> or through pure analog delay stages with large area passives.<sup>42,43</sup> Nonetheless, one of the major advantage of receiver-side equalization is that the filter tap coefficients can be adaptively tuned to the specific channel,<sup>41</sup> which is not possible with transmit-side equalization unless a "back-channel" is implemented.<sup>44</sup>

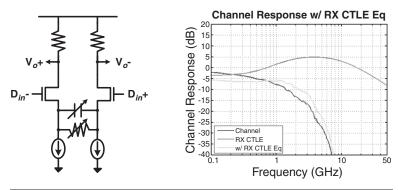

Linear receiver equalization can also be implemented with a continuous-time amplifier, as shown in Fig. 9.18. Here, programmable RC-degeneration in the differential amplifier creates a high-pass filter transfer function that compensates the low-pass channel. While this implementation is a simple and low-area solution, one issue is that the amplifier has to supply gain at frequencies close to the full signal data rate. This gain-bandwidth requirement potentially limits the maximum data rate, particularly in time-division demultiplexing receivers.

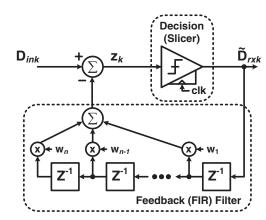

The final equalization topology commonly implemented in high-speed links is receiver-side *decision feedback equalizer* (DFE). A DFE, shown in Fig. 9.19, attempts to directly subtract ISI from the incoming signal by feeding back the resolved data to control the polarity of the equalization taps. Unlike linear receiver equalization, a DFE does not directly amplify the input signal noise or crosstalk since it uses the quantized input values. However, there is the potential for error propagation in a DFE if the noise is large enough for a quantized output to be wrong. Also, due to the feedback equalization structure, the DFE cannot cancel precursor ISI.

The major challenge in DFE implementation is closing timing on the first-tap feedback since this must be done in one bit period or *unit interval* (UI). Direct feedback implementations<sup>3</sup> require this critical timing path to be highly optimized. While a loop-unrolling architecture eliminates the need for first-tap feedback,<sup>45</sup> if multiple-tap

305

FIGURE 9.19 RX equalization with a DFE.

implementation is required, the critical path simply shifts to the second tap, which has a timing constraint also near 1 UI.<sup>5</sup>

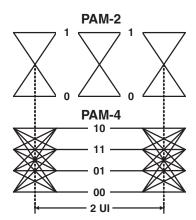

#### 9.3.2 Advanced Modulation Techniques

Modulation techniques that provide spectral efficiencies higher than simple binary signaling have also been implemented by link designers in order to increase data rates over band-limited channels. Multilevel PAM, most commonly PAM-4, is a popular modulation scheme that has been implemented both in academia<sup>46</sup> and in industry.<sup>47,48</sup> Shown in Fig. 9.20, PAM-4 modulation consists of two bits per symbol, which allows transmission of an equivalent amount of data in half the channel bandwidth.

However, due to the transmitter's peak-power limit, the voltage margin between symbols is  $3 \times (9.5 \text{ dB})$  lower with PAM-4 versus simple binary PAM-2 signaling. Thus, a general rule of thumb exists that if the channel loss at the PAM-2 Nyquist frequency is greater than 10 dB relative to the previous octave, then PAM-4 can potentially

Figure 9.20 Pulse amplitude modulation: simple binary PAM-2 (1 bit/symbol) and PAM-4 (2 bits/symbol).

offer a higher *signal-to-noise ratio* (SNR) at the receiver. However, this rule can be somewhat optimistic due to the differing ISI and jitter distribution present with PAM-4 signaling.<sup>37</sup> Also, PAM-2 signaling with a nonlinear DFE at the receiver further bridges the performance gap due to the DFE's ability to cancel the dominant first postcursor ISI without the inherent signal attenuation associated with transmitter equalization.

Another more radical modulation format under consideration by link researchers is the use of multitone signaling. While this type of signaling is commonly used in systems such as DSL modems, <sup>49</sup> it is relatively new for high-speed interchip communication applications. In contrast with conventional baseband signaling, multitone signaling breaks the channel bandwidth into multiple frequency bands over which data is transmitted. This technique has the potential to greatly reduce equalization complexity relative to baseband signaling due to the reduction in per-band loss, and the ability to selectively avoid severe channel nulls.

Typically, in systems such as modems where the data rate is significantly lower than the on-chip processing frequencies, the required frequency conversion is done in the digital domain and requires DAC transmit and ADC receiver front-ends. <sup>50,51</sup> While it is possible to implement high-speed transmit DACs, <sup>52</sup> the excessive digital processing and ADC speed and precision required for multi-Gb/s channel bands results in prohibitive receiver power and complexity. Thus, for power-efficient multitone receivers, researchers have proposed using analog mixing techniques combined with integration filters and *multiple-input/multiple-output* (MIMO) DFEs to cancel out band-to-band interference. <sup>53</sup>

Serious challenges exist in achieving increased interchip communication bandwidth over electrical channels while still satisfying I/O power and density constraints. As discussed, current equalization and advanced modulation techniques allow data rates near 10 Gb/s over severely band-limited channels. However, this additional circuitry comes with a power and complexity cost, with typical commercial high-speed serial I/O links consuming close to 20 mW/Gb/s<sup>33,54</sup> and research-grade links consuming near 10 mW/Gb/s.<sup>14,55</sup> The demand for higher data rates will only result in increased equalization requirements and further degrade link energy efficiencies without improved low-power design techniques. Ultimately, excessive channel loss should motivate investigation into the use of optical links for chip-to-chip applications.

#### 9.4 Low-Power Design Techniques

In order to support the bandwidth demands of future systems, serial link data rates must continue to increase. While the equalization and modulation techniques discussed in the previous section can extend

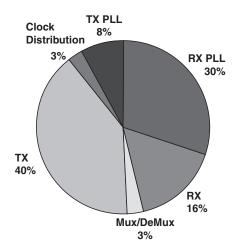

Figure **9.21** 4.8 Gb/s serial link power breakdown. (From Ref. 56.)

data rates over bandwidth-limited channels, the power costs incurred with this additional complexity can be prohibitive without improvements in power efficiency. This section discusses low-power I/O architectures and circuit techniques to improve link power efficiency and enable continued interchip bandwidth scaling in a manner compliant with limited chip power budgets.

Figure 9.21 shows the power breakdown of a 4.8 Gb/s serial link designed for a fully buffered DIMM system, <sup>56</sup> which achieves a power efficiency of 15 mW/Gb/s in a 90-nm technology. For the design, more than 80% of the power is consumed in the transmitter and the clocking system consisting of the *clock multiplication unit* (CMU), clock distribution, and RX-PLL used for timing recovery.

Receiver sensitivity and channel loss set the required transmit output swing, which has a large impact on transmitter power consumption. The receiver sensitivity is set by the input referred offset,  $V_{offset}$ , minimum latch resolution voltage,  $V_{min}$ , and the minimum SNR required for a given BER. Combining these terms results in a total minimum voltage swing per bit of

$$\Delta V_b = \sqrt{SNR}\sigma_n + V_{offset} + V_{min}, \qquad (9.5)$$

where  $\sigma_n^2$  is the total input voltage noise variance. Proper circuit biasing can ensure that the input-referred rms noise voltage is less than 1 mV, and design techniques can reduce the input offset and latch minimum voltage to the 1–2 mV range. Thus, for a BER of  $10^{-12}$  ( $\sqrt{SNR}\cong 7$ ), a sensitivity of less than 20 mV<sub>ppd</sub> (2  $\Delta$ V<sub>b</sub>) is achievable.

While this sensitivity is possible, given the amount of variations in nanometer CMOS technology, it is essential to implement offset correction in order to approach this level. Figure 9.22 shows some common implementations of correction DACs, with adjustable current

FIGURE 9.22 Receiver input offset correction circuitry.

sources producing an input voltage offset to correct the latch offset and digitally adjustable capacitors, skewing the single-ended regeneration time constant of the latch output nodes to perform an equivalent offset cancellation.<sup>30,57</sup>

Leveraging offset correction at the receiver dramatically reduces the required transmit swing, allowing the use of low-swing voltage-mode drivers. As discussed in the link overview section, a differentially terminated voltage-mode driver requires only one-fourth of the current of a current-mode driver in order to produce the same receiver voltage swing. Increased output stage efficiency propagates throughout the transmitter, allowing for a reduction in predriver sizing and dynamic switching power. One of the first examples of the use of a low-swing voltage-mode driver was in Ref. 9, which achieved 3.6 Gb/s at a power efficiency of 7.5 mW/Gb/s in a 0.18-µm technology. A more recent design<sup>15</sup> leveraged a similar design and achieved 6.25 Gb/s at a total link power efficiency of 2.25 mW/Gb/s in a 90-nm technology.

While low-swing voltage-mode drivers can allow for reduced transmit power dissipation, one drawback is that the swing range is limited due to output impedance control constraints. Thus, for links that operate over a wide data rate or channel loss range, the flexibility offered by a current mode driver can present a better design choice. One example of such a design is Ref. 30, which operates over 5–15 Gb/s and achieves 2.8–6.5 mW/Gb/s total link power efficiency in a 65-nm technology while using a scalable current-mode driver. In this design, efficiency gains are made elsewhere by leveraging low-complexity equalization, low-power clocking, and voltage-supply scaling techniques.

With equalization becoming a necessity as data rates scale well past electrical channel bandwidths, the efficiency at which these equalization circuits are implemented becomes paramount. Circuit complexity and bandwidth limitations are present in both transmitter and receiver equalization structures. At the transmitter, increasing the FIR equalization tap number presents power costs due to increased flop count and extra staging logic. While at the receiver, decision feedback equalizers implemented in a direct feedback manner<sup>3</sup> have a 1 UI critical timing path that must be highly optimized. This critical timing path can be relieved with a loop-unrolling architecture for the first tap, <sup>45</sup> but it doubles the number of input comparators and also complicates timing recovery.

Low-complexity active and passive structures are viable equalization topologies that allow for excellent power efficiency. As a receiver input amplifier is often necessary, implementing frequency peaking in this block through RC degeneration is a way to compensate for channel loss with little power overhead. This is observed in recent low-power I/O transceivers, <sup>15,30</sup> which have input CTLE structures. Passive equalization structures, such as shunt inductive termination and tunable passive attenuators, <sup>58</sup> also provide frequency peaking at close to zero power cost.

While CTLE and passive equalization efficiently compensate for high-frequency channel loss, a key issue with these topologies is that the peaking transfer function also amplifies input noise and crosstalk. Also, the input-referred noise of cascaded receiver stages is increased when the DC gain of these input equalizers is less than 1. This is always the case in passive structures that offer no gain and occurs often in CTLE structures that must trade off peaking range, bandwidth, and DC gain. In order to fully compensate for the total channel loss, systems sensitive to input noise and crosstalk may need to also employ higher-complexity DFE circuits, which avoid this noise enhancement by using quantized input values to control the polarity of the equalization taps.

A considerable percentage of total link power is consumed in the clocking systems. One key portion of the clocking power is the receiver timing recovery, where significant circuit complexity and power are used in PLL-based and dual-loop timing recovery schemes. High-frequency clock distribution over multiple link channels is also important, with key trade-offs present between power and jitter performance.

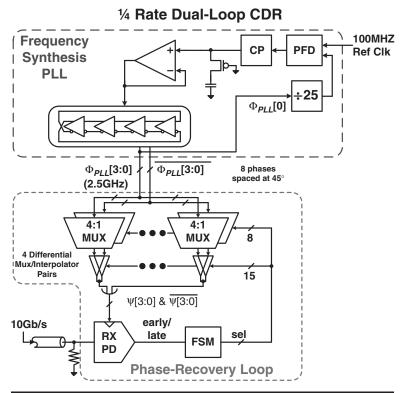

As explained earlier in Sec. 9.2.1, dual-loop CDRs provide the flexibility to optimize for both CDR bandwidth and frequency synthesis noise performance. However, phase resolution and linearity considerations cause the interpolator structures used in these architectures to consume significant power and area. As conventional half-rate receivers using 2×-oversampled phase detectors require two differential interpolators to generate data and quadrature edge sampling clock phases, direct implementations of dual-loop architectures

Figure 9.23 Dual-loop CDR with feedback interpolation [59].

lead to poor power efficiency performance. This has led to architectures that merge the interpolation block into the frequency synthesis loop. 15,59,60

Figure 9.23 shows an implementation where one interpolator is placed in the feedback path of a frequency synthesis PLL in order to produce a high-resolution phase shift simultaneously in all of the VCO multiphase outputs used for data sampling and phase detection. This is particularly beneficial in quarter or eight-rate systems, as only one interpolator is required independent of the input demultiplexing ratio. Recent power-efficient links have further optimized this approach by combining the interpolator with the CDR phase detector. <sup>15,60</sup>

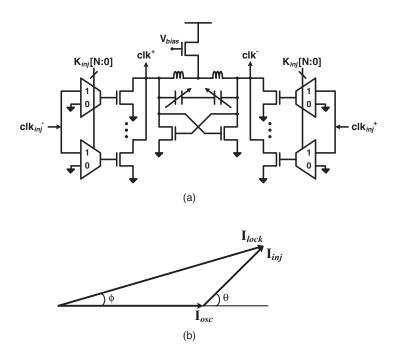

Another low-complexity receiver timing recovery technique suitable for forwarded clock links involves the use of injection-locked oscillators (Fig. 9.24). In this de-skewing technique, the forwarded clock is used as the injection clock to a local oscillator at each receiver. A programmable phase shift is developed by tuning either the injection clock strength or the local receiver oscillator free-running frequency. This approach offers advantages of low complexity, as the clock phases are generated directly from the oscillator without any interpolators, and high-frequency jitter tracking, as the jitter on the forwarded clock is correlated with the incoming data jitter. Recent low-power receivers have been implemented up to 27 Gb/s at an efficiency of 1.6 mW/Gb/s with a local LC oscillator.<sup>61</sup> and 7.2 Gb/s at an efficiency of 0.6 mW/Gb/s with a local ring oscillator.<sup>62</sup>

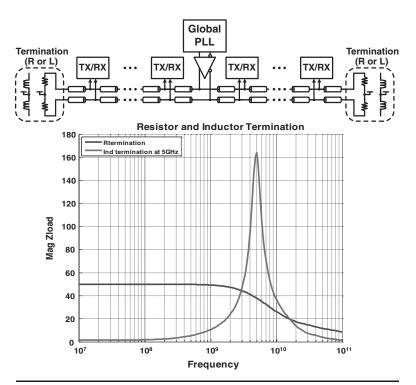

Clock distribution is important in multichannel serial link systems, as the high-frequency clocks from the central frequency synthesis PLL, and the forwarded receive clock in source-synchronous systems, are often routed several millimeters to the transmit and receive channels. Multiple distribution schemes exist, ranging from

Figure 9.24 Injection locked oscillator (ILO) de-skew: (a) LC ILO (from Ref. 61) and (b) ILO vector diagram.

simple CMOS inverters to carefully engineered resonant transmission-line structures, which trade off jitter, power, area, and complexity. There is the potential for significant power cost with active clock distribution, as the buffer cells must be designed with adequate bandwidth to avoid any jitter amplification of the clock signal as it propagates through the distribution network.

One approach to save clock distribution power is the use of ondie transmission lines (Fig. 9.25), which allows for repeaterless clock distribution. An example of this is in the power-efficient link architecture of Ref. 30, which implements transmission lines that have roughly 1 dB/mm loss and are suitable for distributing the clock several millimeters. Further improvements in clock power efficiency are obtained through the use of resonant transmission-line structures. Inductive termination was used to increase transmission-line impedance at the resonance frequency in the system of Ref. 15. This allows for reduced distribution current for a given clock voltage swing. One downside of this approach is that it is narrow-band and not suitable for a system that must operate over multiple data rates.

Serial link circuitry must be designed with sufficient bandwidth to operate at the maximum data rate necessary to support peak system demands. However, during periods of reduced system workload, this excessive circuit bandwidth can translate into a significant amount of

Figure 9.25 Global transmission-line-based clock distribution.

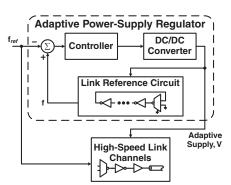

wasted power. Dynamic power management techniques extensively used in core digital circuitry<sup>63</sup> can also be leveraged to optimize serial link power for different system performance.

Adaptively scaling the power supply of the serial link CMOS circuitry to the minimum voltage V required to support a given frequency f can result in quadratic power savings at a fixed frequency or data rate since digital CMOS power is proportional to  $V^2f$ . Nonlinear power savings result with data rate reductions, as the supply voltage can be further reduced to remove excessive timing margin present with the lower-frequency serialization clocks. Increasing the multiplexing factor, for example, using a quarter-rate system versus a half-rate system, can allow for further power reductions, since the parallel transmitter and receiver segments utilize a lower-frequency clock to achieve a given data rate. This combination of adaptive supply scaling and parallelism was used in Ref. 17, which used a multiplexing factor of 5 and a supply range of 0.9–2.5 V to achieve 0.65–5 Gb/s operation at power-efficiency levels ranging from 15 to 76 mW/Gb/s in a 0.25- $\mu$ m process.

Power-scaling techniques were extended to serial link CML circuitry in Ref. 30, which scaled both the power supply and bias currents

313

FIGURE 9.26

Adaptive power supply regulator for high-speed link system.

of replica-based symmetric load amplifiers<sup>20</sup> to achieve linear bandwidth variation at near constant gain. This design achieved 5–15 Gb/s operation at power efficiency levels ranging from 2.7 to 5 mW/Gb/s in a 65-nm process.

In order to fully leverage the benefits of these adaptive power management techniques, the regulator that generates the adaptive supply voltage must supply power to the link at high efficiency. Switching regulators provide a high-efficiency (>90%) means of accomplishing this.<sup>17,29</sup> Figure 9.26 shows a block diagram of a general adaptive power supply regulator, which sets the link supply voltage by adjusting the speed of a reference circuit in the feedback path. This reference circuit should track the link critical timing path, with examples including replicas of the VCO in the link PLL<sup>17</sup> and the TX serializer and output stage predriver.<sup>30</sup>

#### 9.5 Optical Interconnects

Increasing interchip communication bandwidth demand has motivated investigation into using optical interconnect architectures over channel-limited electrical counterparts. Optical interconnects with negligible frequency-dependent loss and high bandwidth<sup>64</sup> provide viable alternatives to achieving dramatic power efficiency improvements at per-channel data rates exceeding 10 Gb/s. This has motivated extensive research into optical interconnect technologies suitable for high-density integration with CMOS chips.

Conventional optical data transmission is analogous to wireless AM radio, where data is transmitted by modulating the optical intensity or amplitude of the high-frequency optical carrier signal. In order to achieve high fidelity over the most common optical channel, the glass fiber, high-speed optical communication systems typically use infrared light from source lasers with wavelengths ranging from 850 nm to 1550 nm, or equivalently frequencies ranging from 200 Thz to 350 THz. Thus, the potential data bandwidth is quite large since

this high optical carrier frequency exceeds current data rates by over three orders of magnitude.

Moreover, because the loss of typical optical channels at short distances varies only fractions of decibels over wide wavelength ranges (tens of nanometers),<sup>65</sup> there is the potential for data transmission of several terabits per second without the requirement of channel equalization. This simplifies design of optical links in a manner similar to non–channel-limited electrical links. However, optical links do require additional circuits that interface to the optical sources and detectors. Thus, in order to achieve the potential link performance advantages, emphasis is placed on using efficient optical devices and low-power and area interface circuits.

This section gives an overview of the key optical link components, beginning with the optical channel attributes. Optical devices, drivers, and receivers suited for low-power high-density I/O applications are presented. The section concludes with a discussion of optical integration approaches, including hybrid optical interconnect integration where the CMOS I/O circuitry and optical devices reside on different substrates and integrated CMOS photonic architectures, which allow for dramatic gains in I/O power efficiency.

#### 9.5.1 Optical Channels

The two optical channels relevant for short distance chip-to-chip communication applications are *free-space* (air or glass) and *optical fibers*. These optical channels offer potential performance advantages over electrical channels in terms of loss, crosstalk, and both physical interconnect and information density.<sup>64</sup>

Free-space optical links have been used in applications ranging from long-distance line-of-sight communication between buildings in metro-area networks<sup>66</sup> to short-distance interchip communication systems.<sup>67–69</sup> Typical free-space optical links use lenses to collimate light from a laser source. After collimated, laser beams can propagate over relatively long distances due to narrow divergence angles and low atmospheric absorption of infrared radiation. The ability to focus short-wavelength optical beams into small areas avoids many of the crosstalk issues faced in electrical links and provides the potential for very high information density in free-space optical interconnect systems with small two-dimensional (2D) transmit and receive arrays. 67,70,71 However, free-space optical links are sensitive to alignment tolerances and environmental vibrations. To address this, researchers have proposed rigid systems with flip-chip bond chips onto plastic or glass substrates with 45° mirrors or diffractive optical elements<sup>69</sup> that perform optical routing with very high precision.

Optical fiber-based systems, while potentially less dense than free-space systems, provide alignment and routing flexibility for

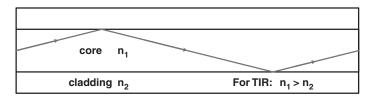

FIGURE 9.27 Optical fiber cross-section.

chip-to-chip interconnect applications. An optical fiber, shown in Fig. 9.27, confines light between a higher index core and a lower index cladding via total internal reflection. In order for light to propagate along the optical fiber, the interference pattern, or mode, generated from reflecting off the fiber's boundaries must satisfy resonance conditions. Thus, fibers are classified based on their ability to support multiple or single modes.

Multimode fibers with large core diameters (typically 50 or 62.5  $\mu m)$  allow several propagating modes, and thus are relatively easy to couple light into. These fibers are used in short- and medium-distance applications such as parallel computing systems and campus-scale interconnection. Often relatively inexpensive vertical-cavity surface-emitting lasers (VCSEL) operating at wavelengths near 850 nm are used as the optical sources for these systems. While fiber loss ( $\sim\!3$  dB/km for 850 nm light) can be significant for some low-speed applications, the major performance limitation of multimode fibers is modal dispersion caused by the different light modes propagating at different velocities. Due to modal dispersion, multimode fiber is typically specified by a bandwidth-distance product, with legacy fiber supporting 200 MHz-km and current optimized fiber supporting 2 GHz-km.  $^{72}$

Single-mode fibers with smaller core diameters (typically 8–10  $\mu m)$  only allow one propagating mode (with two orthogonal polarizations), and thus require careful alignment in order to avoid coupling loss. These fibers are optimized for long-distance applications such as links between Internet routers spaced up to and exceeding 100 km. Fiber loss typically dominates the link budgets of these systems, and thus they often use source lasers with wavelengths near 1550 nm which match the loss minima ( $\sim\!0.2$  dB/km) of conventional single-mode fiber. While modal dispersion is absent from single-mode fibers, chromatic dispersion (CD) and polarization-mode dispersion (PMD) exists. However, these dispersion components are generally negligible for distances less than 10 km and are not issues for short-distance interchip communication applications.

Fiber-based systems provide another method of increasing the optical channel information density: *wavelength division multiplexing* (WDM). WDM multiplies the data transmitted over a single channel

by combining several light beams of differing wavelengths that are modulated at conventional multi-Gb/s rates onto one fiber. This is possible due to the several terahertz of low-loss bandwidth available in optical fibers. While conventional electrical links which employ baseband modulation do not allow this type of wavelength or frequency division multiplexing, WDM is analogous to the electrical link multitone modulation mentioned in Sec. 9.3.2 However, the frequency separation in the optical domain uses passive optical filters<sup>73</sup> rather than the sophisticated DSP techniques required in electrical multitone systems.

In summary, both free-space and fiber-based systems are applicable for chip-to-chip optical interconnects. For both optical channels, loss is the primary advantage over electrical channels. This is highlighted by comparing the highest optical channel loss, present in multimode fiber systems ( $\sim$ 3 dB/km), to typical electrical backplane channels at distances approaching only 1 m (>20 dB at 5 GHz). Also, because pulse-dispersion is small in optical channels for distances appropriate for chip-to-chip applications (<10 m), no channel equalization is required. This is in stark contrast to the equalization complexity required by electrical links due to the severe frequency-dependent loss in electrical channels.

#### 9.5.2 Optical Transmitter Technology

Optical links with multiple gigabits per second exclusively use coherent laser light due to its low divergence and narrow wavelength range. Modulation of this laser light is possible by directly modulating the laser intensity through changing the laser's electrical drive current or by using separate optical devices to externally modulate laser light via absorption changes or controllable phase shifts that produce constructive or destructive interference. The simplicity of directly modulating a laser allows a huge reduction in the complexity of an optical system because only one optical source device is necessary. However, this approach is limited by laser bandwidth issues and, while not necessarily applicable to short-distance chip-to-chip I/O, the broadening of the laser spectrum, or "chirp," that occurs with changes in optical power intensity results in increased chromatic dispersion in fiber systems. External modulators are not limited by the same laser bandwidth issues and generally do not increase light linewidth. Thus, for long-haul systems where precision is critical, all links generally use a separate external modulator that changes the intensity of a beam from a source laser, often referred to as continuous-wave (CW), operating at a constant power level.

In short-distance interchip communication, cost constraints outweigh precision requirements, and systems with direct and externally modulated sources have both been implemented. Directly modulated lasers and optical modulators, both electroabsorption and refractive, have been proposed as high-bandwidth optical sources, with these different sources displaying trade-offs in both device and circuit driver efficiency. Vertical-cavity surface-emitting lasers<sup>74</sup> are an attractive candidate due to their ability to directly emit light with low-threshold currents and reasonable slope efficiencies; however, their speed is limited by both electrical parasitics and carrier–photon interactions.

A device that does not display this carrier speed limitation is the electroabsorption modulator, based on either the *quantum-confined Stark effect* (QCSE)<sup>75</sup> or the Franz–Keldysh effect,<sup>76</sup> which is capable of achieving acceptable contrast ratios at low drive voltages over tens of nanometers of optical bandwidth. Ring resonator modulators<sup>77,78</sup> are refractive devices that display very high resonant quality factors and can achieve high-contrast ratios with small dimensions and low capacitance; however, their optical bandwidth is typically less than 1 nm. Another refractive device capable of wide optical bandwidth (>100 nm) is the Mach–Zehnder modulator<sup>79</sup>; however, this comes at the cost of a large device and high voltage swings. All of the optical modulators also require an external source laser and incur additional coupling losses relative to a VCSEL-based link.

#### **Vertical-Cavity Surface-Emitting Laser (VCSEL)**

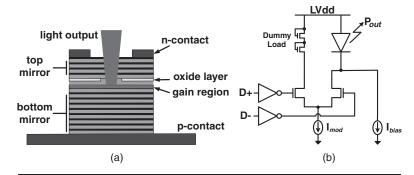

A *vertical-cavity surface-emitting laser* (VCSEL), shown in Fig. 9.28 (a), is a semiconductor laser diode that emits light perpendicular from its top surface. These surface-emitting lasers offer several manufacturing advantages over conventional edge-emitting lasers, including wafer-scale testing ability and dense 2D array production. The most common VCSELs are GaAs-based operating at 850 nm, <sup>80–82</sup> with 1310 nm GaInNAs-based VCSELs in recent production, <sup>83</sup> and research-grade devices near 1550 nm. <sup>84</sup>

Current-mode drivers are often used to modulate VCSELs due to the device's linear optical power–current relationship. A typical VCSEL output driver is shown in Fig. 9.28 (b), with a differential stage steering current between the optical device and a dummy load, and an additional static current source used to bias the VCSEL

**Figure 9.28** Vertical-cavity surface-emitting laser: (a) device cross-section and (b) driver circuit.

sufficiently above the threshold current,  $I_{th}$ , in order to ensure adequate bandwidth.

While VCSELs appear to be the ideal source due to their ability to both generate and modulate light, serious inherent bandwidth limitations and reliability concerns do exist. A major constraint is the bandwidth  $BW_{VCSEL}$ , which is dependent on the average current  $I_{avg}$  flowing through it:

$$BW_{VCSEL} \propto \sqrt{I_{avg} - I_{th}}$$

(9.6)

Unfortunately, output power saturation due to self-heating<sup>85</sup> and also device lifetime concerns<sup>86</sup> restrict excessive increase of VCSEL average current levels to achieve higher bandwidth. As data rates scale, designers have begun to implement simple transmit equalization circuitry to compensate for VCSEL electrical parasitics and reliability constraints.<sup>87–89</sup>

#### **Electro-Absorption Modulator (EAM)**

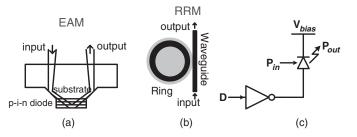

An *electro-absorption modulator* (EAM) is typically made by placing an absorbing quantum-well region in the intrinsic layer of a PIN diode. In order to produce a modulated optical output signal, light originating from a continuous-wave source laser is absorbed in an EA modulator depending on electric field strength through electro-optic effects such as the quantum-confined Stark effect or the Franz–Keldysh effect. These devices are implemented either as a waveguide structure, <sup>76,90,91</sup> where light is coupled in and travels laterally through the absorbing *multiple-quantum-well* (MQW) region, or as a surface-normal structure, <sup>75,92–94</sup> where incident light performs one or more passes through the MQW region before being reflected out.

While large contrast ratios are achieved with waveguide structures, there are challenges associated with dense 2D implementations due to poor misalignment tolerance (due to difficulty coupling into the waveguides) and somewhat large size (>100  $\mu m$ ). Surface-normal devices are better suited for high-density 2D optical interconnect applications due to their small size (~10  $\times$  10  $\mu m$  active area) and improved misalignment tolerance [Fig. 9.29 (a)]. However, as the light travels only a short distance through the absorbing MQW regions, there are challenges in obtaining required contrast ratios.

These devices are typically modulated by applying a static positive bias voltage to the n-terminal and driving the p-terminal between Gnd and Vdd, often with simple CMOS buffers [Fig. 9.29 (c)]. The ability to drive the small surface-normal devices as an effective lumped-element capacitor offers a huge power advantage when compared to larger waveguide structures, since the  $CV^2f$  power is relatively low due to small-device capacitance, whereas waveguide structures are typically driven with traveling wave topologies that often require low-impedance termination and a relatively large amount of switching

#### High-Speed Serial I/O Design

**Figure 9.29** External modulators: (a) Electro-absorption modulator<sup>94</sup>; (b) ring-resonator modulator; (c) driver circuit.

current.<sup>91</sup> However, due to the light only traveling a limited distance in the MQW region, the amount of contrast ratio that surface-normal structures achieve with CMOS-level voltage swings is somewhat limited, with a typical contrast ratio near 3 dB for 3 V swing.<sup>94</sup> While recent work has been done to lower modulator drive voltages near 1 V,<sup>75</sup> robust operation requires swings larger than predicted CMOS supply voltages in future technology nodes.<sup>6</sup> One circuit that allows for this in a reliable manner is a pulsed-cascode driver,<sup>95</sup> which offers a voltage swing of twice the nominal supply while using only core devices for maximum speed.

#### Ring Resonator Modulator (RRM)

Ring resonator modulators (RRMs) [Fig. 9.29 (b)] are refractive devices that achieve modulation by changing the interference of the light coupled into the ring with the input light on the waveguide. They use high confinement resonant ring structures to circulate the light and increase the optical path length without increasing the physical device length, which leads to strong modulation effects even with ring diameters less than 20 µm. 96 Devices that achieve a refractive index change through carrier injection into PIN diode structures<sup>96</sup> allow for integration directly onto silicon substrates with the CMOS circuitry. An alternative integration approach involves fabricating the modulators in an optical layer on top of the integrated circuit metal layers, 97 which saves active silicon area and allows for increased portability of the optical technology nodes due to no modifications in the front-end CMOS process. One example of this approach included *electro-optic* (EO) polymer cladding ring resonator modulators, <sup>78</sup> which operate by shuttling carriers within the molecular orbital of the polymer chromophores to change the refractive index.

In addition to using these devices as modulators, ring resonators can also realize optical filters suitable for *wavelength division multiplexing* (WDM), which allows for a dramatic increase in the bandwidth density of a single optical waveguide.<sup>97</sup> Due to the ring resonator modulator's high selectivity, a bank of these devices can independently modulate several optical channels placed on a waveguide from

a multiple-wavelength source. Similarly, at the receiver side, a bank of resonators with additional "drop" waveguides can perform optical demultiplexing to separate photodetectors.

Ring resonator modulators are relatively small and can be modeled as a simple lumped element capacitor with values less than 10 fF for sub-30  $\mu m$  ring radius devices. This allows the use of nonimpedance-controlled voltage-mode drivers similar to the EA modulator drivers of Fig. 9.29 (c). While the low capacitance of the ring resonators allows for excellent power efficiency, the devices do have very sharp resonances ( $\sim 1~\text{nm})^{98}$  and are very sensitive to process and temperature variations. Efficient feedback tuning circuits and/or improvements in device structure to allow less sensitivity to variations are needed to enhance the feasibility of these devices in high-density applications.

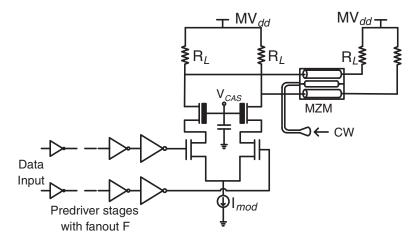

#### Mach-Zehnder Modulator (MZM)

Mach–Zehnder modulators (MZMs) are also refractive modulators that work by splitting the light to travel through two arms where a phase shift is developed that is a function of the applied electric field. The light in the two arms is then recombined either in phase or out of phase at the modulator output to realize the modulation. MZMs that use the free-carrier plasma-dispersion effect in p–n diode devices to realize the optical phase shift have been integrated in CMOS processes and have recently demonstrated operation in excess of 10 Gbps. <sup>79,99</sup> The modulator transfer characteristic with half-wave voltage  $V_{\pi}$  is

$$\frac{P_{out}}{P_{in}} = 0.5 \left( 1 + \sin \frac{\pi V_{swing}}{V_{\pi}} \right) \tag{9.7}$$

Figure 9.30 shows an MZM transmitter schematic. <sup>99</sup> Unlike smaller modulators, which are treated as lumped capacitive loads, due to MZM length ( $\sim$ 1 mm), the differential electrical signal is distributed using a pair of transmission lines terminated with low impedance. In order to achieve the required phase shift and reasonable contrast ratio, long devices and large differential swings are required, necessitating a separate voltage supply  $MV_{dd}$ . Thick-oxide cascode transistors are used to avoid stressing driver transistors with the high supply.

#### 9.5.3 Optical Receiver Technology

Optical receivers generally determine the overall optical link performance, since their sensitivity sets the maximum data rate and amount of tolerable channel loss. Typical optical receivers use a photodiode to sense the high-speed optical power and produce an input current. This photocurrent is then converted to a voltage and amplified sufficiently for data resolution. In order to achieve increasing data rates, sensitive high-bandwidth photodiodes and receiver circuits are necessary.

FIGURE 9.30 Mach-Zehnder modulator driver circuit.

High-speed PIN photodiodes are typically used in optical receivers due to their high responsivity and low capacitance. In the most common device structures, normally incident light is absorbed in the intrinsic region of width W, and the generated carriers are collected at the reverse-bias terminals, thereby causing an effective photocurrent to flow. The amount of current generated for a given input optical power  $P_{opt}$  is set by the detector's responsivity

$$\rho = \frac{I}{P_{opt}} = \frac{\eta_{pd} \lambda q}{hc} = 8 \times 10^5 \left( \eta_{pd} \lambda \right) (\text{mA/mW}), \qquad (9.8)$$

where  $\lambda$  is the light wavelength and the detector quantum efficiency  $\eta_{\textit{pd}}$  is

$$\eta_{pd} = 1 - e^{-\alpha W},\tag{9.9}$$

where here  $\alpha$  is the detector's absorption coefficient. Thus, an 850-nm detector with sufficiently long intrinsic width W has a responsivity of 0.68 mA/mW. In well-designed photodetectors, the bandwidth is set by the carrier transit time  $\tau_{tr}$  or saturation velocity  $v_{sat}$ ,

$$f_{3dBPD} = \frac{2.4}{2\pi\tau_{tr}} = \frac{0.45v_{sat}}{W}$$

(9.10)

From Eqs. (9.9) and (9.10), an inherent trade-off exists in normally incident photodiodes between responsivity and bandwidth due to their codependence on the intrinsic region width W, with devices designed above 10 GHz generally unable to achieve maximum responsivity. Therefore, in order to achieve increased data rates while still maintaining high responsivity, alternative photodetector structures are

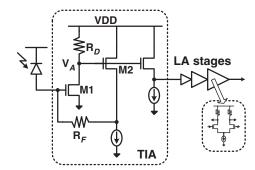

FIGURE 9.31

Optical receiver

with TIA input

stage and following

limiting amplifier

(LA) stages.

proposed such as the trench detector<sup>101</sup> or lateral *metal*—*semiconductor*—*metal* (MSM) detectors.<sup>102</sup>

In traditional optical receiver front-ends, a *transimpedance amplifier* (TIA) converts the photocurrent into a voltage and is followed by limiting amplifier stages that provide amplification to levels sufficient to drive a high-speed latch for data recovery (Fig. 9.31). Excellent sensitivity and high bandwidth can be achieved by TIAs that use a negative feedback amplifier to reduce the input time constant.<sup>73,103</sup>

Unfortunately, while process scaling has been beneficial to digital circuitry, it has adversely affected analog parameters such as output resistance, which is critical to amplifier gain. Another issue arises from the inherent transimpedance limit, 104 which requires the gain-bandwidth of the internal amplifiers used in TIAs to increase as a quadratic function of the required bandwidth in order to maintain the same effective transimpedance gain.

While the use of peaking inductors can allow bandwidth extension for a given power consumption,  $^{103,104}$  these high area passives lead to increased chip costs. These scaling trends have reduced TIA efficiency, thereby requiring an increasing number of limiting amplifier stages in the receiver front-end to achieve a given sensitivity and leading to excessive power and area consumption.

A receiver front-end architecture that eliminates linear high-gain elements, and thus is less sensitive to the reduced gain in modern processes, is the integrating and double-sampling front-end. The absence of high-gain amplifiers allows for savings in both power and area and makes the integrating and double-sampling architecture advantageous for chip-to-chip optical interconnect systems where retiming is also performed at the receiver.

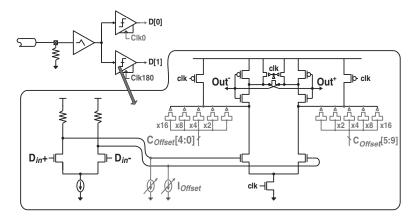

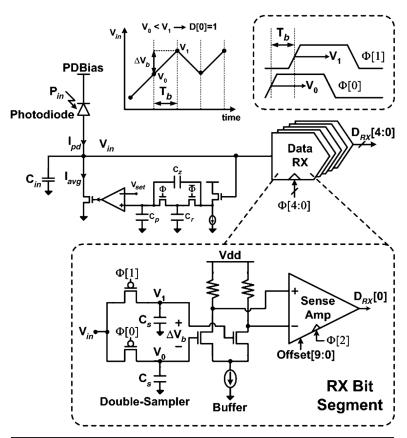

The integrating and double-sampling receiver front-end, shown in Fig. 9.32, demultiplexes the incoming data stream with five parallel segments that include a pair of input samplers, a buffer, and a sense-amplifier. Two current sources at the receiver input node—the photodiode current and a current source that is feedback-biased to the average photodiode current—supply and deplete charge from the receiver input capacitance, respectively.

## High-Speed Serial I/O Design

FIGURE 9.32 Integrating and double-sampling the receiver front-end.

For data encoded to ensure DC balance, the input voltage will integrate up or down due to the mismatch in these currents. A differential voltage,  $\Delta V_b$ , that represents the polarity of the received bit is developed by sampling the input voltage at the beginning and end of a bit period defined by the rising edges of the synchronized sampling clocks  $\Phi[n]$  and  $\Phi[n+1]$  that are spaced a bit-period,  $T_b$ , apart. This differential voltage is buffered and applied to the inputs of an offset-corrected sense-amplifier,  $^{12}$  which is used to regenerate the signal to CMOS levels.

The optimum optical receiver front-end architecture is a function of the input capacitance breakdown between lumped capacitance sources, such as the photodetector, bond pads, and wiring, and the amplifier's input capacitance for a TIA front-end or the sampling capacitor sizes for an integrating front-end. In a TIA front-end, optimum sensitivity is achieved by lowering the input referred noise through increasing the amplifier's input transistors' transconductance up to the point at which the input capacitance is near the lumped capacitance

components,  $^{106}$  while for an integrating front-end, increasing the sampling capacitor size reduces kT/C noise at the cost of also reducing the input voltage swing, with an optimum sampling capacitor size less than the lumped input capacitance.  $^{107}$  The use of waveguide-coupled photodetectors  $^{102,108}$  developed for integrated CMOS photonic systems, which can achieve sub-10 fF capacitance values, can result in the circuit input capacitance dominating over the integrated photodetector capacitance. This results in a simple resistive front-end achieving optimum sensitivity.  $^{108}$

#### 9.5.4 Optical Integration Approaches

Efficient cost-effective integration approaches are necessary for optical interconnects to realize their potential to increase per-channel data rates at improved power-efficiency levels. This involves engineering the interconnect between the electrical circuitry and optical devices in a manner that minimizes electrical parasitic, optimizing the optical path for low loss, and choosing the most robust and power-efficient optical devices.

#### **Hybrid Integration**

*Hybrid integration* schemes. with the optical devices fabricated on a separate substrate, are generally considered the most feasible in the near term, since this allows optimization of the optical devices without any impact on the CMOS process. With hybrid integration, methods to connect the electrical circuitry to the optical devices include wire bonding, flip-chip bonding, and short in-package traces.

Wire bonding offers a simple approach suitable for low-channel count stand-alone optical transceivers, <sup>109,110</sup> since having the optical VCSEL and photodetctor arrays separated from the main CMOS chip allows for simple coupling into a ribbon fiber module. However, the wire bonds introduce inductive parasitics and adjacent channel crosstalk. Moreover, the majority of processors today are packaged with flip-chip bonding techniques.

Flip-chip bonding optical devices directly to CMOS chips dramatically reduce interconnect parasitics. One example of a flip-chip-bonded optical transceiver is discussed in Ref. 111, which bonds an array of 48 bottom-emitting VCSELs (12 VCSELS at four different wavelengths) onto a 48-channel optical driver and receiver chips. The design places a parallel multiwavelength optical subassembly on top of the VCSEL array and implements WDM by coupling the 48 optical beams into a 12-channel ribbon fiber.

A drawback of this approach is that the light is coupled out of the top of the VCSEL array bonded onto the CMOS chip. This implies that the CMOS chip cannot be flip-chip-bonded inside a package, and all signals to the main chip must therefore be connected via wire bonding, which can limit power delivery.

A solution to this problem is presented in the approach of Ref. 112, which flips the main CMOS chip with bonded VCSELs onto a silicon carrier. This carrier includes through-silicon vias to connect signals to the main CMOS chip and a cavity for the optical element array. Light is coupled out normally from the chip via 45° mirrors that perform an optical 90° turn into optical waveguides embedded in a board for chip-to-chip routing. While flip-chip bonding does allow for minimal interconnect parasitic, concerns about VCSEL reliability necessitate careful thermal management due to close thermal coupling of the VCSEL array and the CMOS chip.

An alternative approach that is compatible with flip-chip bonding packaging is to flip-chip bond both the main CMOS chip and the optical device arrays to the package and then use short electrical traces between the CMOS circuitry and the optical device array. This technique allows for top-emitting VCSELs, 113 with the VCSEL optical output coupled via 45° mirrors that perform an optical 90° turn into optical waveguides embedded in the package for coupling into a ribbon fiber for chip-to-chip routing.

#### **Integrated CMOS Photonics**

While hybrid integration approaches allow for per-channel data rates well in excess of 10 Gbps, parasitics associated with the off-chip interconnect and bandwidth limitations of VCSELs and PIN photodetectors can limit both the maximum data rate and power efficiency. Tightly integrating the photonic devices with the CMOS circuitry dramatically reduces bandwidth-limiting parasitics and allows the potential for I/O data rates to scale proportionally with CMOS technology performance. Integrated CMOS photonics also offers a potential system cost advantage, as reducing discrete optical components count simplifies packaging and testing.

Optical waveguides are used to route the light between the photonic transmit devices, filters, and photodetectors in an integrated photonic system. If the photonic devices are fabricated on the same layer as the CMOS circuitry, these waveguides can be realized in an SOI process as silicon core waveguides cladded with SiO<sub>2</sub><sup>73,96</sup> or in a bulk CMOS process as poly-silicon core waveguides with the silicon substrate etched away to produce an air gap underneath the waveguide to prevent light leakage into the substrate. <sup>114</sup> For systems with the optical elements fabricated in an optical layer on top of the integrated circuit metal layers, waveguides have been realized with silicon <sup>115</sup> or SiN cores. <sup>97</sup>

Ge-based waveguide-coupled photodetectors compatible with CMOS processing have been realized with area less than  $5\,\mu m^2$  and capacitance less than  $1\,fF.^{102}$  The small area and low capacitance of these waveguide photodetectors allow for tight integration with CMOS receiver amplifiers, resulting in excellent sensitivity.  $^{108}$

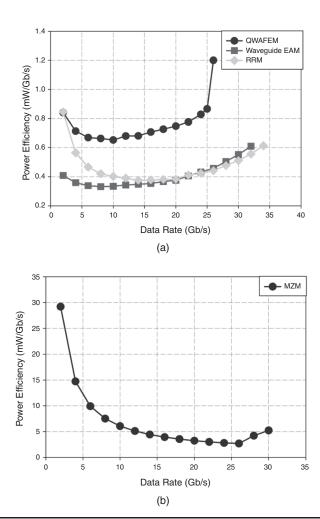

FIGURE 9.33 Integrated optical transceiver power efficiency modeled in 45-nm CMOS (clocking excluded): (a) QWAFEM EAM (from Ref. 75), waveguide EAM (from Ref. 76), polymer RRM (from Ref. 78) and (b) MZM (from Ref. 79).

Integrated CMOS photonic links are currently predominately modulator-based, as an efficient silicon-compatible laser has yet to be implemented. Electro-absorption,<sup>75,76</sup> ring-resonator,<sup>96,97</sup> and Mach–Zehnder<sup>73,79</sup> modulators have been proposed, with the different devices offering trade-offs in optical bandwidth, temperature sensitivity, and power efficiency.

Figure 9.33 compares the power efficiency of integrated CMOS photonic links modeled in a 45-nm CMOS process. <sup>116</sup> The small size of the electro-absorption and ring-resonator devices results in low capacitance and allows for simple nonterminated voltage mode-drivers which translates into excellent power efficiency. An advantage of the

RRM over the EAM is that the RRM may also serve as optical filters for WDM systems. However, the RRM is extremely sensitive to temperature due to the high-Q resonance, necessitating additional thermal tuning. Mach–Zehnder modulators achieve operation over a wide optical bandwidth and are thus less sensitive to temperature. However, the size of typical devices necessitates transmitter circuitry that can drive transmission lines terminated in a low impedance, resulting in high power. Significant improvements are required for the MZM to obtain lower  $V_{\pi}$  and better power efficiency.