#### ECEN620: Network Theory Broadband Circuit Design Fall 2014

#### Lecture 7: Phase Detector Circuits

#### Sam Palermo Analog & Mixed-Signal Center Texas A&M University

#### Announcements & Agenda

- HW2 is due Oct 6

- Exam 1 is on Wed. Oct 8

- Covers Lectures 1-6

- One double-sided 8.5x11 notes page allowed

- Bring your calculator

- Previous exams are posted for reference

- Phase Detector Circuits

- Mixer PD

- XOR PD

- J-K Flip-Flop PD

- Phase-Frequency Detector (PFD)

#### References

- *RF Microelectronics,* B. Razavi, Prentice Hall, 1998.

- Design of Integrated Circuits for Optical Communications, B. Razavi, McGraw-Hill, 2003.

- *Monolithic Phase-Locked Loops and Clock Recovery Circuits,* B. Razavi, Wiley, 1996.

- M. Perrott, *High Speed Communication Circuits and Systems Course*, MIT Open Courseware

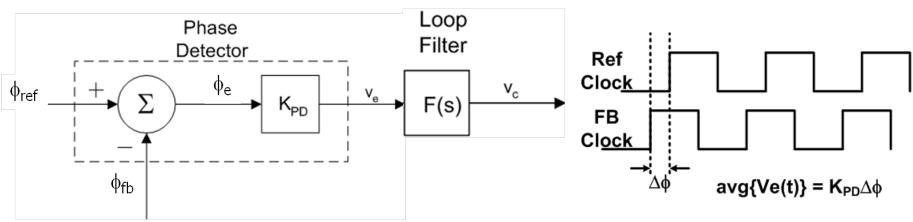

#### Phase Detector

- Detects phase difference between feedback clock and reference clock

- The loop filter will filter the phase detector output, thus to characterize phase detector gain, extract average output voltage

- The K<sub>PD</sub> factor can change depending on the specific phase detector circuit

$K_{PD}$  units are V/rad when used with a dimension - less filter

$K_{PD}$  units are rad<sup>-1</sup> (averaged) or A/rad when combined with the charge - pump

when used with a impedance filter

avg{Ve(t)}

**K**PD

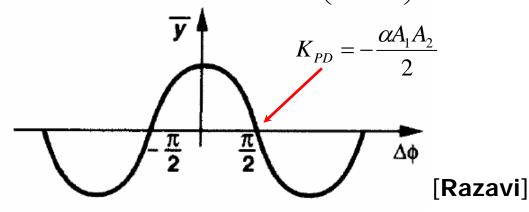

#### Analog Multiplier Phase Detector

$$A_{1}\cos\omega_{1}t \longrightarrow \frac{\alpha A_{1}A_{2}}{2}\cos[(\omega_{1}+\omega_{2})t+\Delta\phi] + \frac{\alpha A_{1}A_{2}}{2}\cos[(\omega_{1}-\omega_{2})t-\Delta\phi]$$

$$A_{2}\cos(\omega_{2}t+\Delta\phi) \qquad \alpha \text{ is mixer gain}$$

• If  $\omega_1 = \omega_2$  and filtering out high-frequency term

$$\overline{y(t)} = \frac{\alpha A_1 A_2}{2} \cos \Delta \phi$$

• Near  $\Delta \phi$  lock region of  $\pi/2$ :  $\overline{y(t)} \approx \frac{\alpha A_1 A_2}{2} \left( \frac{\pi}{2} - \Delta \phi \right)$

### **Analog Mixer PD Properties**

- The nominal lock point (zero frequency offset or Type-2) with a mixer PD is a 90° static phase shift

- For many applications this is unimportant or can be cancelled elsewhere

- The mixer cannot serve as a frequency detector, as on average the output will be zero for a frequency difference

- K<sub>PD</sub> is a function of the input amplitude, which is not desired

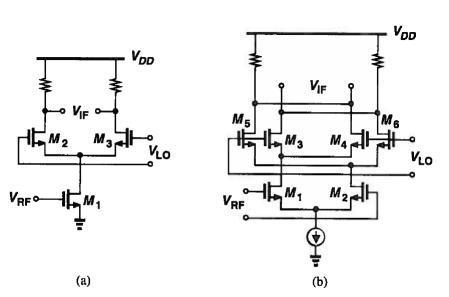

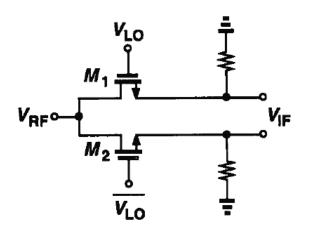

#### Mixer Circuits

**Active Mixers**

#### Passive Mixer

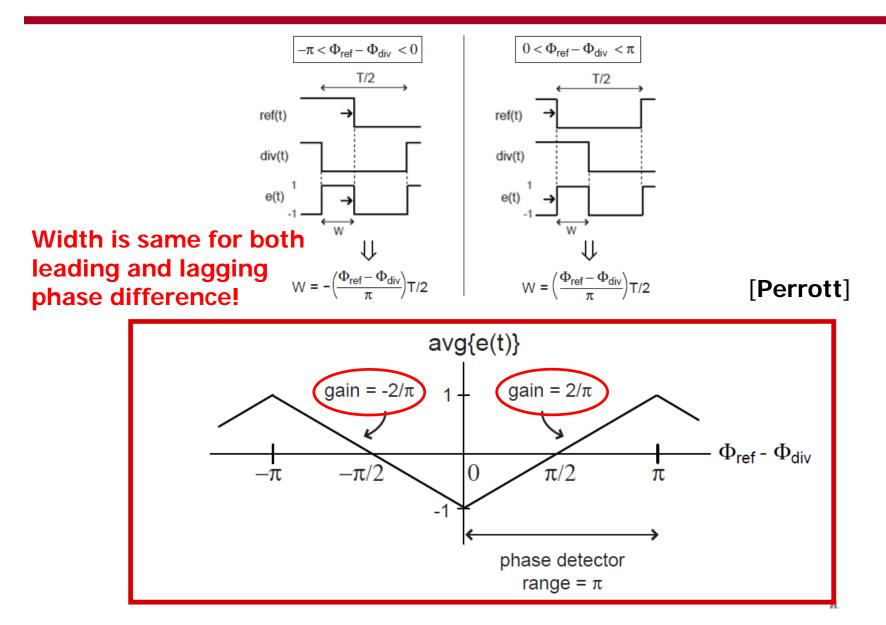

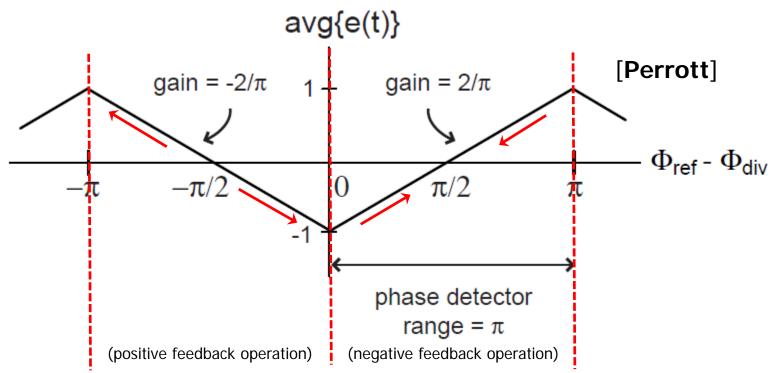

#### **XOR Phase Detector**

- Assuming logic 1="+1" and 0="-1", the XOR PD will lock when the average output is 0

- Generally,  $\pi/2$  is a stable lock point and  $-\pi/2$  is a metastable point

- Sensitive to clock duty cycle

#### **XOR Phase Detector**

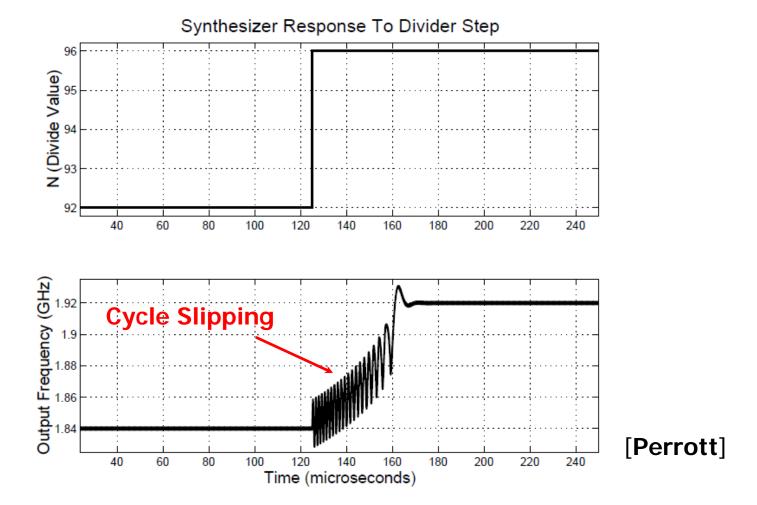

# Cycle Slipping

- If there is a frequency difference between the input reference and PLL feedback signals the phase detector can jump between regions of different gain

- PLL is no longer acting as a linear system

# Cycle Slipping

• If frequency difference is too large the PLL may not lock

#### **XOR PD Properties**

- The nominal lock point with an XOR PD is also a 90° static phase shift

- Unlike the analog mixer,  $K_{PD}$  is independent of input amplitude and constant over a  $\pi$  phase range

- The XOR PD is sensitive to input duty cycle, and will lock with a phase error if the input duty cycles are not 50%

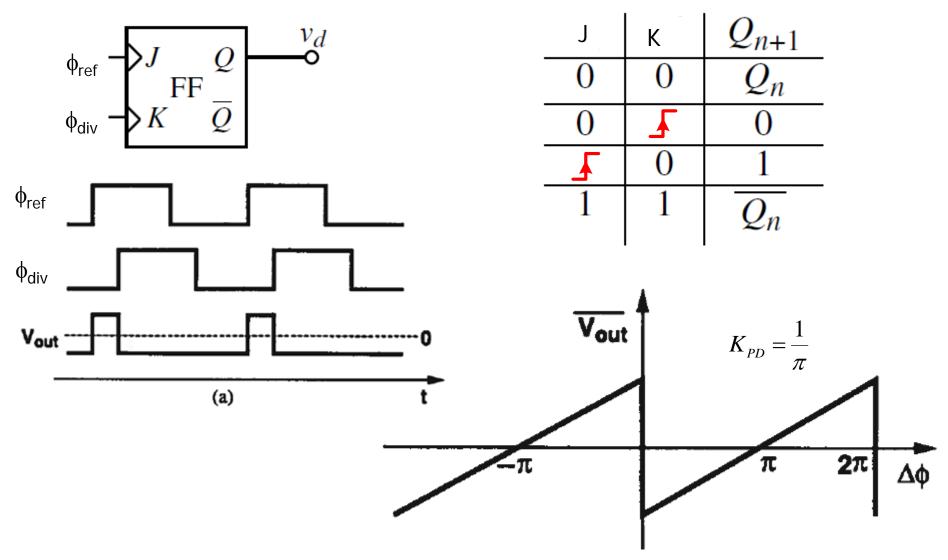

#### J-K Flip-Flop Phase Detector

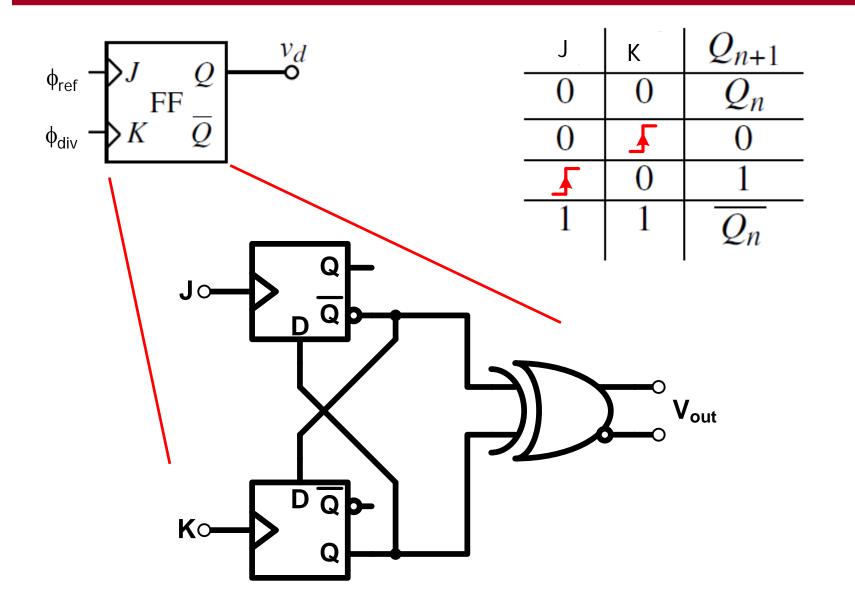

#### J-K Flip-Flop Details

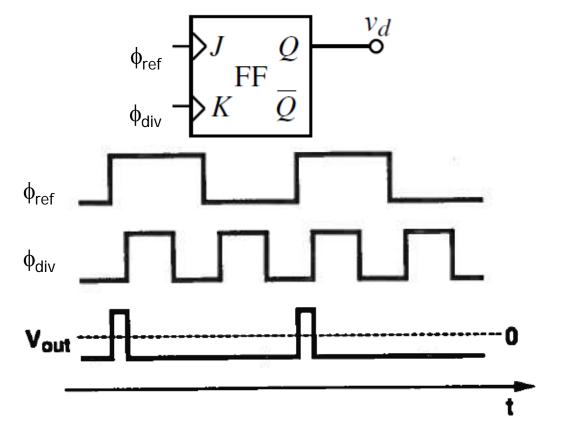

#### J-K Flip-Flop Phase Detector Harmonic Locking

Harmonic signals can display the same DC output, leading to potential locking to harmonics

## J-K Flip-Flop PD Properties

- The nominal lock point with an J-K Flip-Flop PD is a 180° static phase shift

- The J-K Flip-Flop PD is not sensitive to input duty cycle

- The J-K Flip-Flop displays a constant KPD over a  $2\pi$  range

- There is the potential to lock to harmonics of the reference clock

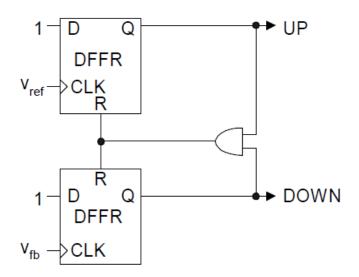

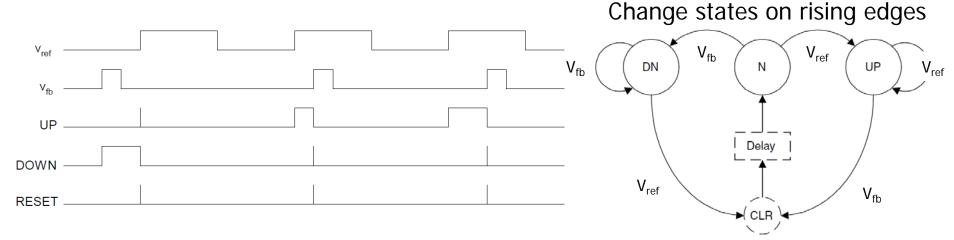

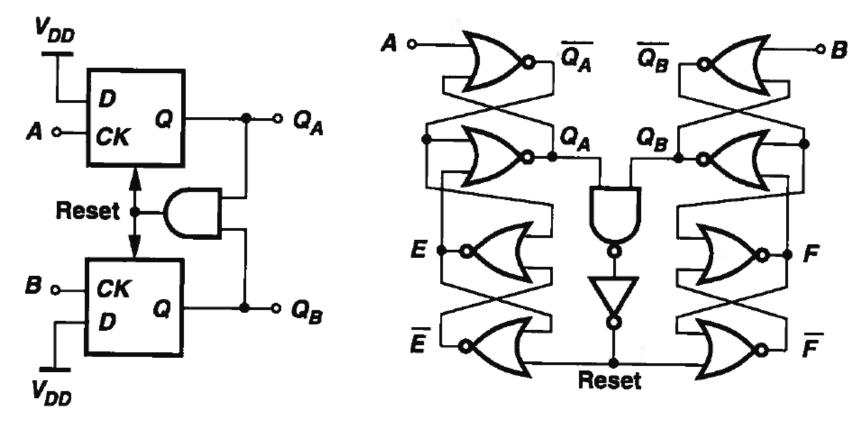

## Phase Frequency Detector (PFD)

- Phase Frequency Detector allows for wide frequency locking range, potentially entire VCO tuning range

- 3-stage operation with UP and DOWN outputs

- Edge-triggered results in duty cycle insensitivity

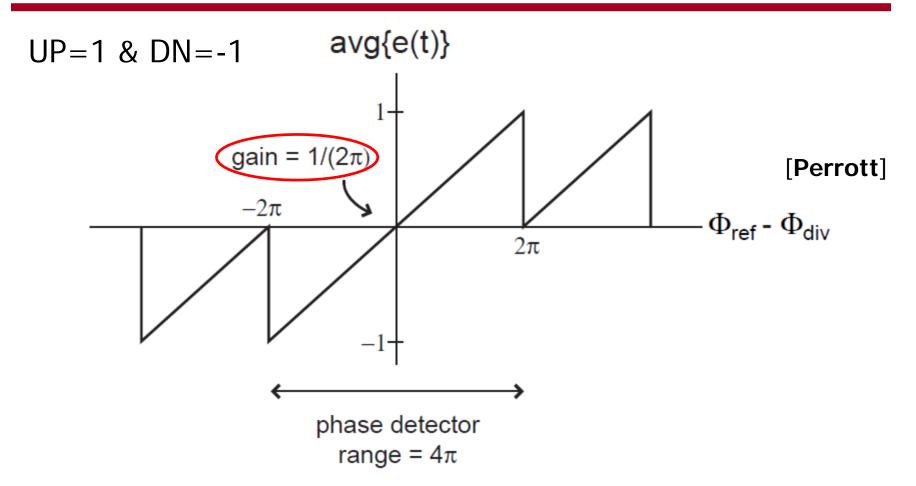

#### PFD Transfer Characteristic

• Constant slope and polarity asymmetry about zero phase allows for wide frequency range operation

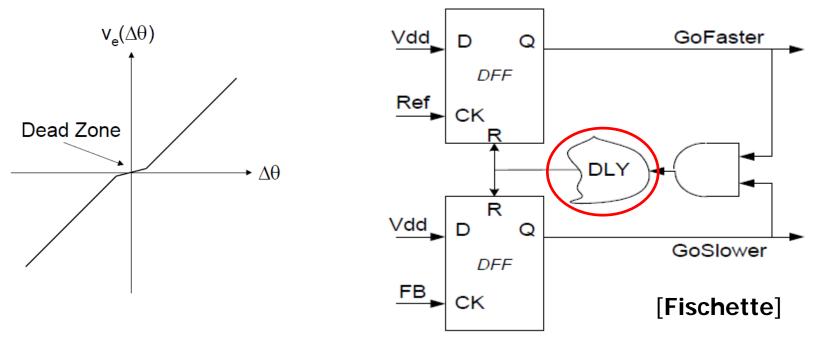

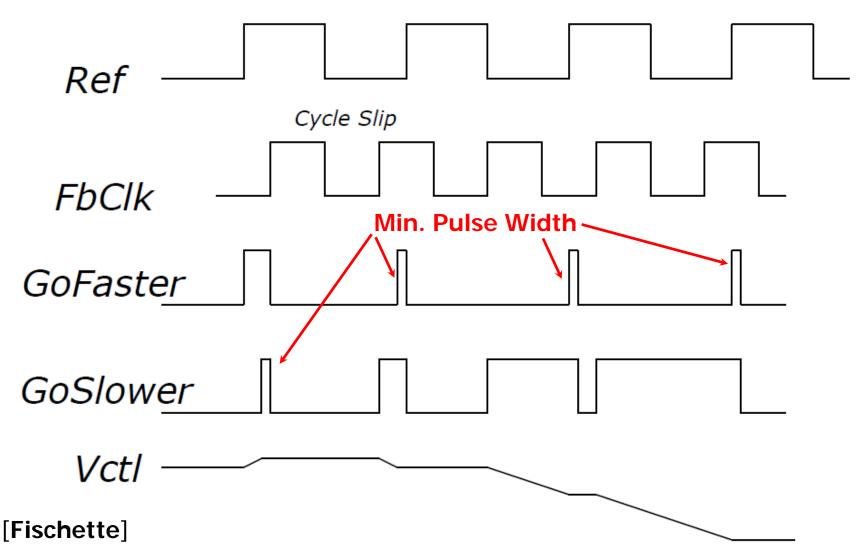

#### PFD Deadzone

- If phase error is small, then short output pulses are produced by PFD

- Cannot effectively propagate these pulses to switch charge pump

- Results in phase detector "dead zone" which causes low loop gain and increased jitter

- Solution is to add delay in PFD reset path to force a minimum UP and DOWN pulse length

### **PFD** Operation

### **PFD** Properties

- The nominal lock point with a PFD is 0°

- The PFD is not sensitive to input duty cycle

- The PFD outputs "UP" and "DN" are not complementary and stay high until reset by the other, allowing for efficient frequency detection

- Near lock, the propagation of narrow pulses to switch the charge pump can cause a phase detector "dead zone"

- To prevent this, extra delay is generally inserted in the PFD reset path

#### **Detailed Optimized PFD Schematic**

Because the flip-flop data input is always "1", the logic can be optimized for higher speed operation

#### Next Time

Charge Pump Circuits