# Texas A&M University Department of Electrical and Computer Engineering

## ECEN 620 – Network Theory (Broadband Circuit Design)

## Fall 2022

## Exam #1

#### Instructor: Sam Palermo

- Please write your name in the space provided below

- Please verify that there are 6 pages in your exam

- You may use <u>one</u> double-sided page of notes and equations for the exam

- Good Luck!

| Problem | Score | Max Score |

|---------|-------|-----------|

| 1       |       | 50        |

| 2       |       | 50        |

| Total   |       | 100       |

SAM PALERMO Name:

UIN:\_\_\_\_\_

•

#### Problem 1 (50 points)

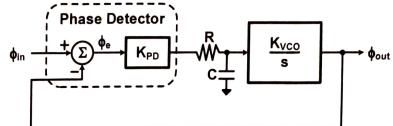

For the PLL block diagram shown below, assume that the phase detector gain is  $K_{PD}$  and the VCO gain is  $K_{VCO}$ .

a) Find the expressions for the open loop gain, LG(s), the closed-loop transfer function  $H(s)=\phi_{out}(s)/\phi_{in}(s)$ , and the phase error transfer function,  $E(s)=\phi_e(s)/\phi_{in}(s)$ . (30 points)

$$LG(S) = \frac{K_{PO}K_{VO}/(RC)}{S(S + \frac{1}{RC})}$$

$$H(s) = \frac{LG(s)}{[+LG(s)]} = \frac{K_{PO}K_{VLO}/(RC)}{s^2 + \frac{s}{RC} + \frac{K_{PO}K_{VLO}}{RC}}$$

$$E(s) = \frac{1}{1 + LG(s)} = \frac{s(s + \frac{1}{Rc})}{s^2 + \frac{s}{Rc} + \frac{k_{PD}k_{RC}}{Rc}}$$

LG(s) =

$H(s) = \phi_{out}(s)/\phi_{in}(s) =$

$E(s)=\phi_e(s)/\phi_{in}(s)=$

b) Assume that  $K_{PD}=2/\pi$  and  $R=1k\Omega$ . Give the values of  $K_{VCO}$  and the loop filter capacitor C for a  $\zeta=1$  and steady-state phase error of  $(\pi/10)$  rad, with a 1Mrad/s frequency step. (10 points)

For Strady-state phase error

$$\frac{1}{4req}$$

step

$\Phi_{e,ss} = \lim_{S \to 0} \left(\frac{\Delta \omega}{s^2}\right)(sE(s)) = \frac{\Delta \omega}{s^2} \frac{s^2(s+\frac{1}{R_c})}{s^2+\frac{s}{R_c}+\frac{keoKreo}{R_c}} = \frac{\Delta \omega}{K_{AD}K_{VO}}$

$\frac{k_{vo}}{k_{oo}} = \frac{\Delta \omega}{k_{oo}} \frac{1}{4e_{ss}} = \frac{1}{(\frac{2}{17})(\frac{\pi}{10})} = 5 \frac{M'ad}{s}$

For  $h = 1 \Longrightarrow$  From H(s) denominator  $2h\omega_n = \frac{1}{R_c}$  and  $\omega_n^2 = \frac{k_{oo}k_{VO}}{R_c}$

$2\sqrt{1}\sqrt{\frac{krok_{VO}}{R_c}} = \frac{1}{R_c} \Longrightarrow C = \frac{1}{(2h)^2 k_{eo}k_{VO}K_{VO}} = \frac{1}{(2\cdot1)^2 (\frac{2}{\pi})(sm)(h)} \frac{k_{vo}}{k_{vo}} = 78.5\rhoF$

$C = 78.5\rhoF$

c) Now assume that  $K_{VCO}$  is modified to improve the steady-state phase error to ( $\pi/100$ ) rad. with a 1Mrad/s frequency step. Using the same R and C numerical values from part(b), what is the new  $\zeta$ ? (5 points)

For

$$\frac{T}{100}$$

phase error  $\Rightarrow$   $K_{VLO, NEV} = 10.$   $K_{VLO, OLD}$

$\int_{1}^{1} = \left(\frac{1}{2}\right) \left(\frac{1}{\sqrt{K_{PD}} K_{VLO} R_{C}}\right) = \frac{1}{\sqrt{10}} = \frac{1}{\sqrt{10}} = 0.316$

5= 0.316

d) Qualitatively comment on how the accuracy of the steady-state phase error with a frequency step impacts the PLL stability. (5 points)

Problem 2 (50 points)

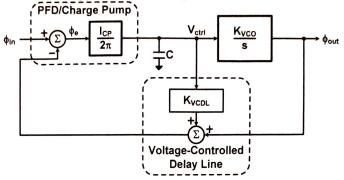

This problem analyzes a PLL with a voltage-controlled delay line (VCDL) in the feedback path. The VCDL can be modeled as adding phase in the feedback path with a certain gain factor  $K_{VCDL}$  (rad/V).

a) Find the expressions for the open loop gain, LG(s), the phase error transfer function, E(s)=\$\phi\_e(s)\$/\$\phi\_in(s), and the closed-loop transfer function H(s)=\$\phi\_out(s)\$/\$\phi\_in(s). (25 points)

$$LG(S) = \frac{I_{cp}}{2\pi} \left(\frac{1}{Sc}\right) \left[\frac{K_{Vco}}{S} + K_{Vcol}\right] = \frac{2\pi c}{S^2} \left[\frac{S + K_{Vcol}}{S^2}\right]$$

$$E(s) = \frac{1}{1 + LG(s)} = \frac{s^2}{s^2 + \frac{T_{cP}K_{kc0L}}{2\pi c}s + \frac{T_{cP}K_{vc0}}{2\pi c}}$$

$$H(s) = \frac{\frac{1}{2\pi}\left(\frac{1}{s_c}\right)\left(\frac{K_{vc0}}{s}\right)}{1 + LG(s)} = \frac{\frac{1}{2\pi}\left(\frac{1}{s_c}\right)\left(\frac{K_{vc0}}{s}\right)}{2\pi c} = \frac{\frac{1}{2\pi}\left(\frac{1}{s_c}\right)\left(\frac{K_{vc0}}{s}\right)}{2\pi c}$$

LG(s) =

$E(s)=\phi_e(s)/\phi_{in}(s)=$

$H(s)=\phi_{out}(s)/\phi_{in}(s)=$

. ..

b) Assume that K<sub>PD</sub>=10µA/(2π), K<sub>VCO</sub>=100Mrad/(sV), and K<sub>VCDL</sub>=10rad/V. Find the value of the loop filter capacitor C for a 45° phase margin. (20 points)

$$PM = 3 - LG(jwu) - (-180^{\circ}) = 45^{\circ}$$

$+an^{-1} \left( \frac{Wu KvceL}{Kvco} \right) - 180^{\circ} + 180^{\circ} = 45^{\circ}$

$$W_{u} = \frac{K_{vco}}{K_{vcor}} + a_{1} (45^{\circ}) = \frac{100 M^{10} Sv}{10 M} = 10^{m} Ccc^{1}$$

- C= 2.25pF

- c) Qualitatively comment on the main differences between this PLL with a VCDL in the feedback path and the conventional charge-pump PLL with a series RC loop filter. Which architecture provides more filtering to high-frequency input phase noise? (5 points)