## Texas A&M University Department of Electrical and Computer Engineering

ECEN 620 - Network Theory (Broadband Circuit Design)

Fall 2020

Exam #1

Instructor: Sam Palermo

- Please write your name in the space provided below

- Please verify that there are 6 pages in your exam

- You may use one double-sided page of notes and equations for the exam

- Good Luck!

| Problem | Score     | Max Score |  |  |

|---------|-----------|-----------|--|--|

| 1       |           | 40        |  |  |

| 2       | J. 1      | 60        |  |  |

| Total   | Carrie of | 100       |  |  |

| Name: S | AM PA | LERMO | ). |  |

|---------|-------|-------|----|--|

| UIN:    |       |       |    |  |

Problem 1 (40 points)

Select the proper PLL architecture to track a frequency ramp of  $10^{12}$  rad/s<sup>2</sup> with a steady-state phase error of 0.01 rad. Assume that  $K_{VCO}=2\pi*(1GHz/V)$  and that the loop filter utilizes a 1nF capacitor. Additional circuitry should be added to the loop filter to achieve a  $\zeta=2$ . Give the value of  $K_{PD}$  (include correct units), draw the loop filter and label the filter component values.

units), draw the loop filter and label the litter component values.

A 213-Order Type I PLL is required to trock a treplancy ramp

$$E(S) = \frac{S^2}{S^2 + 2l_1 N_1 S + U_n^2}$$

Frequency Ramp:  $\phi_{in}(S) = \frac{\Lambda}{S^5}$

$$\phi_{e, 1S} = \frac{l_{in}}{S^3} = \frac{\Lambda}{S^2 + 2l_1 N_1 S + U_n^2} = \frac{\Lambda}{W_1} = 0.01 \text{ rad}$$

$$\Rightarrow U_n = \frac{\Lambda}{\Phi_{e, 1S}} = \frac{\Lambda}{0.01 \text{ rad}} = \frac{10^{77} \text{ rad}}{0.01 \text{ rad}}$$

$$W_n = \sqrt{\frac{KpO kro}{E}}$$

$$K_{pD} = \frac{U_n^2 C}{K_{VLO}} = \frac{(10^{716} M_B^2)^2 (l_n F)}{2\pi (16 He/V)} = \frac{100 \mu A}{2\pi I}$$

$$K_{pD} = \frac{100 \mu A}{2\pi I}$$

$$K_{pD} = \frac{100 \mu A}{2\pi I}$$

$$L_{op} Filter: \frac{1}{2} 400 \pi$$

## Problem 2 (60 points)

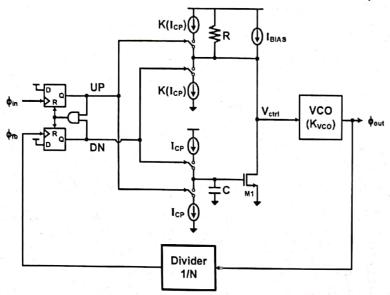

For the PLL shown below, assume that the VCO gain is  $K_{VCO}$  is positive, all transistors are operating in saturation with  $r_0=\infty$  and you can ignore any transistor device capacitors.

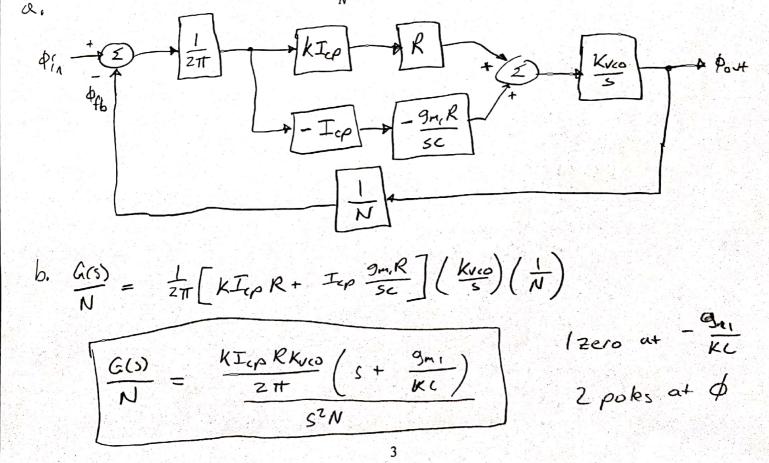

- a) Draw the phase domain small signal model of the loop.

- b) Find the expressions for the product of the forward path gain and feedback factor,  $\frac{G(s)}{N}$ , and determine the pole-zero locations of  $\frac{G(s)}{N}$ .

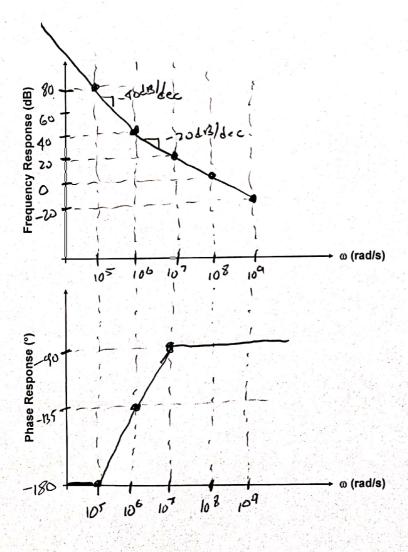

c) Assume that  $I_{CP}=10\mu A$ , K=10,  $R=50k\Omega$ ,  $K_{VCO}=2\pi*(1GHz/V)$ ,  $g_{m1}=20\mu A/V$  and N=50. What is the C value required for the  $\frac{G(s)}{N}$  transfer function zero,  $\omega_z$ , to equal 1Mrad/s? Sketch the  $\frac{G(s)}{N}$  Bode Plot (magnitude and phase). What is the phase margin?

$$C = 2\rho F$$

Phase Margin =  $90^{\circ}$

d) What is the phase relationship between  $\phi_{in}$  and  $\phi_{fb}$  when is PLL locked?

Due to the PFO, the loop will lock with a 0° phase difference.

$\phi_{in} - \phi_{fb} = \bigcirc$

Scratch Paper